Preparation method of field blocking type bipolar transistor of insulated gate

A bipolar transistor, insulated gate technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of complex sheet process operations, high fragmentation rate, and high process costs.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

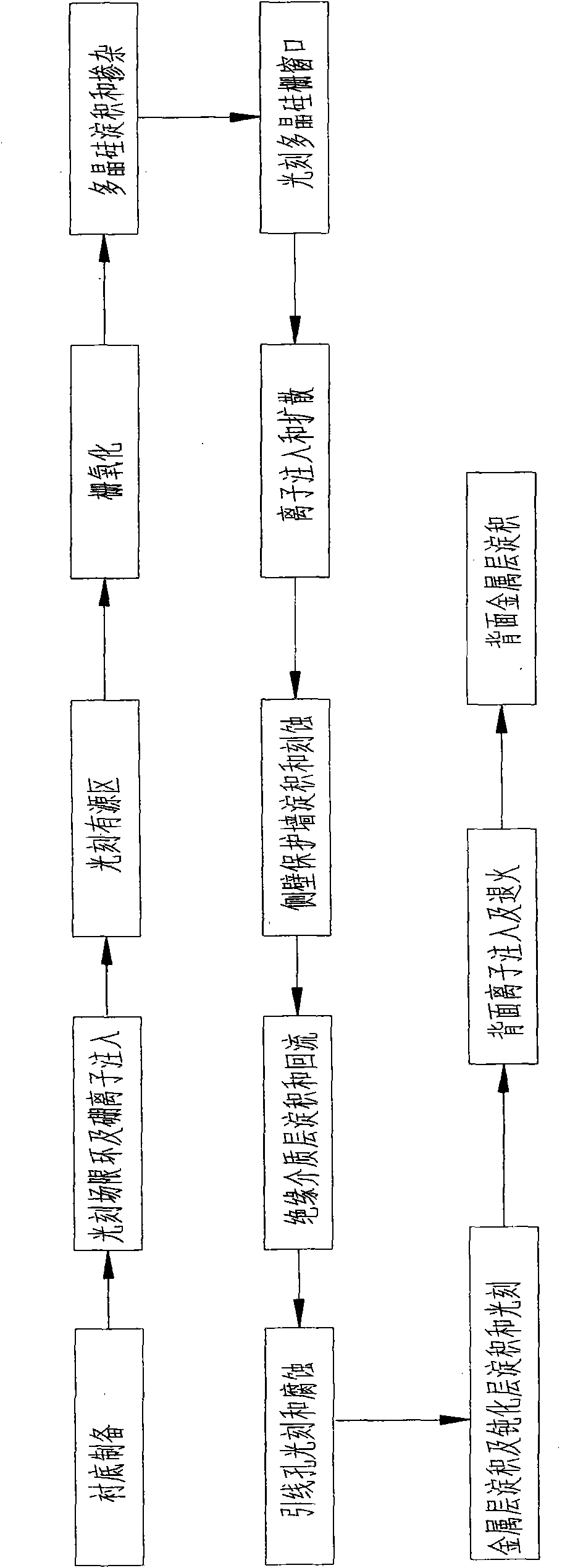

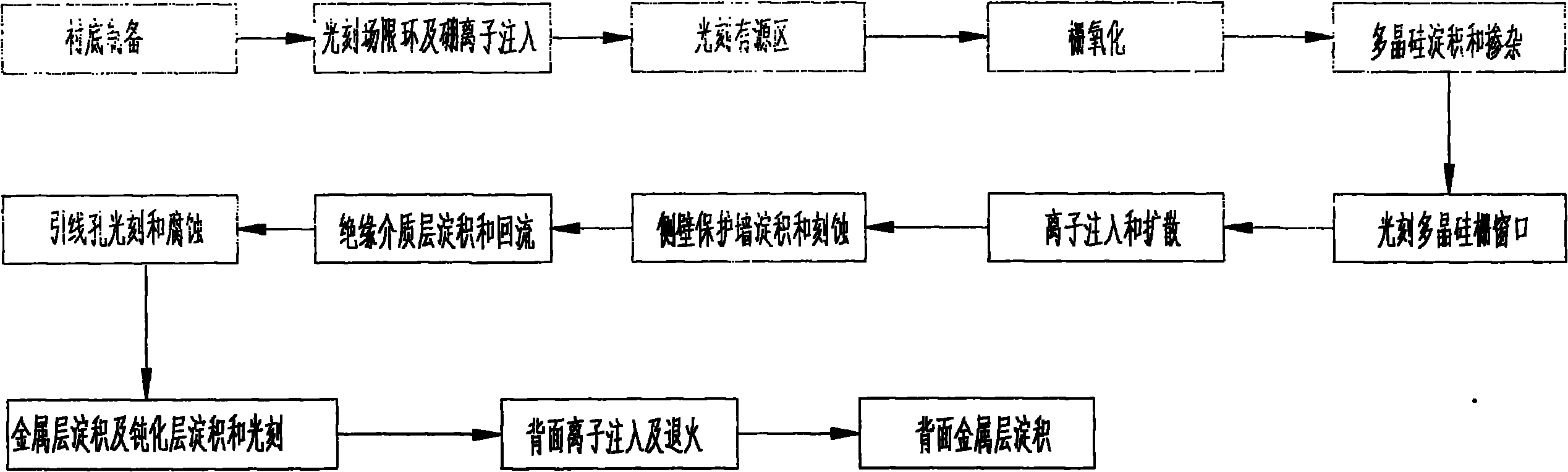

[0023] See image 3 As shown, the method for preparing a field-stop type insulated gate bipolar transistor of the present invention comprises the following steps:

[0024] (1) Substrate preparation: After cleaning the N-type single wafer with a thickness of 100-1000 μm, the resistivity of the N-type single wafer is 10-300Ω·cm, Pre-diffusion of N+-type semiconductor impurities on the surface with a concentration higher than that of N- single wafers can be pre-diffused with a phosphorus source, and then at a temperature of 1100-1300°C, the main diffusion of N+-type impurities is performed for 100-400h, and the junction depth is pushed to 10-300μm Form the N+ impurity region. In the main diffusion of the N+ type impurity in the present invention, the N+ type impurity diffusion can be carried out at a temperature of 1150-1250°C for 150-200h, and the junction depth can be pushed to 50-200μm to form the N+ impurity region. The formed oxide layers on both sides can prevent a large a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More