Multi-circle arranged IC (integrated circuit) chip packaging member and producing method thereof

A technology of chip package and production method, which is applied in the direction of electrical components, electric solid devices, semiconductor devices, etc., can solve the problems that cannot satisfy ultra-thin package products, cannot meet high density, affect high-frequency applications, etc., and achieve signal transmission Fast, good thermal performance, short heat conduction distance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0054] (1), wafer thinning thickness 250μm

[0055] Coarse grinding thickness range, from original wafer to final thickness + adhesive film thickness + 50 μm, rough grinding speed 5 μm / s; fine grinding thickness range, from final thickness + adhesive film thickness + 50 μm to final wafer thickness + adhesive film thickness , Grinding speed: 0.4μm / s, wafer thinning method ordinary QFN thinning, 6-inch to 8-inch wafer VG-502MKⅡ8B automatic thinning machine, 8-inch to 12-inch wafer adopts PG300RM / TCN;

[0056] (2), scribing

[0057] Wafers up to 8 inches use DISC3350 or double-knife dicing machines, and wafers from 8 inches to 12 inches use A-WD-300TXB dicing machines. Application of anti-fragmentation and anti-crack scribing software control technology, the scribing speed is controlled at ≤10mm / s;

[0058] (3), single chip flip chip and reflow soldering

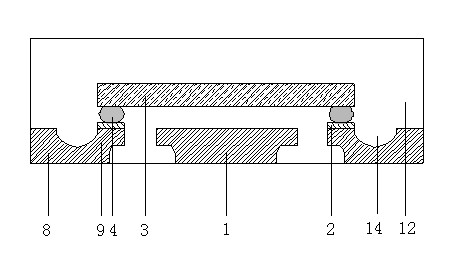

[0059] Single-chip flip-chip bonding, using IC chip 3 with bumps, flip-chip bonding is performed on a carrier frame with a...

Embodiment 2

[0075] (1), wafer thinning thickness 250μm

[0076] Coarse grinding thickness range, from original wafer to final thickness + adhesive film thickness + 50μm, rough grinding speed 2μm / s; fine grinding thickness range, from final thickness + adhesive film thickness + 50μm to final wafer thickness + adhesive film thickness , Grinding speed: 0.9μm / s, ordinary QFN thinning method for wafer thinning, VG-502MKⅡ8B automatic thinning machine for 6-inch to 8-inch wafers, PG300RM / TCN for 8-inch to 12-inch wafers;

[0077] (2) Scribing

[0078] With embodiment 1;

[0079] (3), single chip flip chip and reflow soldering

[0080] With embodiment 1;

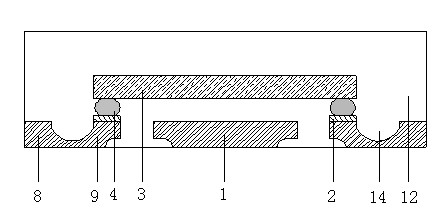

[0081] (4), bottom filling

[0082] Choose a material with a low thermal expansion coefficient, heat the underfill to 80°C, use vacuum technology to underfill the bumps 4 and the pins in the frame, and finally bake the finished product after the underfill in a QFN general-purpose baking oven Bake for about 15 minutes;

[0083] (5)~(7)

...

Embodiment 3

[0092] (1)~(7)

[0093] With embodiment 1;

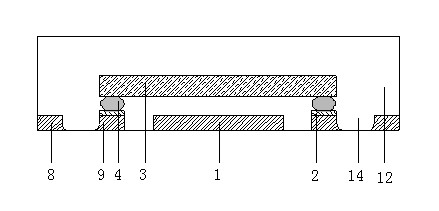

[0094] (8), separate pins

[0095] The pins are separated from each other by laser cutting method, and the cutting depth is 0.13μm;

[0096] (9), electroplating

[0097] The electroplating is the same as that of ordinary QFN packages, and the electroless plating system is directly plated with 7μm pure tin, and the baking conditions and methods after electroless plating are the same as those of ordinary QFN packages after electroplating;

[0098] (10), cutting and separating products

[0099] With embodiment 1.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More