Novel Back Structure of Insulated Gate Bipolar Transistor and Its Fabrication Method

A bipolar transistor, backside structure technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem of on-state voltage drop and low switching loss, which is difficult to coordinate, multi-sub-injection efficiency, and on-state voltage drop. Advanced problems, to achieve the effect of solving ohmic contact and low injection efficiency, precise control of hole distribution, and improving breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

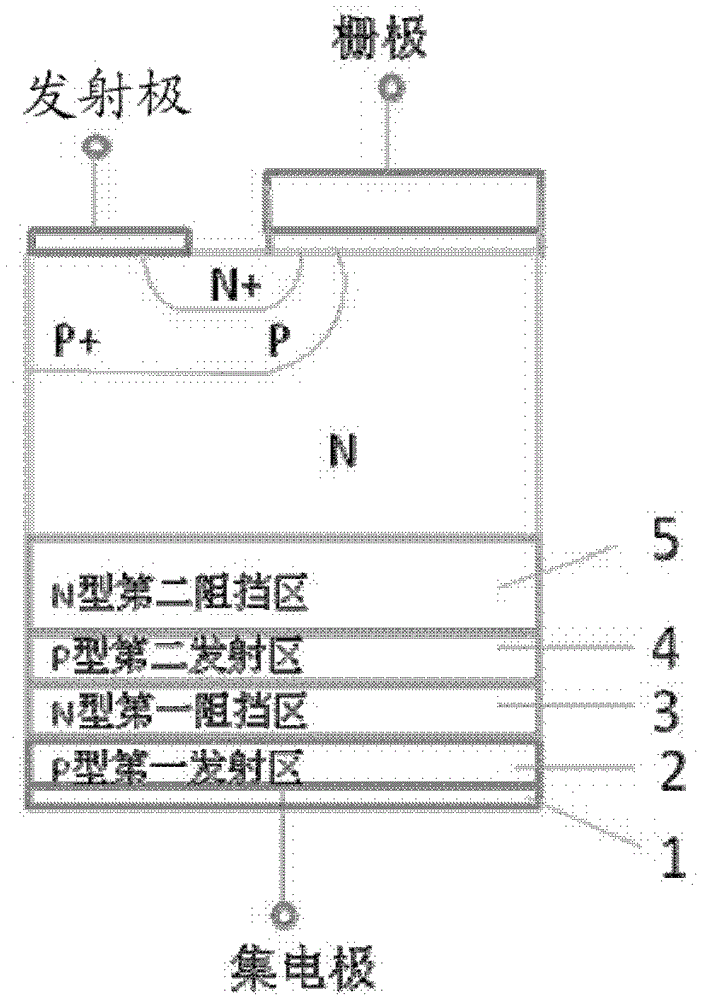

[0025] See image 3 As shown, it is the back structure of the novel insulated gate bipolar transistor of the present invention. The back of the silicon chip of the insulated gate bipolar transistor is sequentially connected with an N-type second barrier region 5, a P-type second emitter region 4, and an N-type first emitter region. Barrier region 3 and P-type first emitter region 2 and collector electrode 1, that is, the back structure is P / N / P / N + A structure combining multi-level emission regions and barrier regions, the thickness of the N-type second barrier region 5 is 0-10 μm, and the thickness can be controlled at 0.1 μm, 0.5 μm, 1 μm, 2 μm, 4 μm, 5 μm, 8 μm, 9 μm, 10 μm etc., preferably controlled between 0.1-5 μm, the injection efficiency of the above-mentioned two-stage emission region can be adjusted through the N-type second barrier region, and the electric field from the front can be blocked at the same time. The thickness of the P-type second emitter region 4 of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More