FPGA (field-programmable gate array) interconnection structure supporting time division switching

A technology of time-division switching and interconnection structure, applied in the FPGA field, can solve problems such as difficult implementation, slow logic circuit performance, increased chip area and power consumption, etc., to solve scalability problems, solve signal stability, and reduce design complexity sexual effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0059] The solutions of the present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

[0060] In order to make the traditional FPGA structure support time-division switching, several major changes need to be made to the existing traditional FPGA structure:

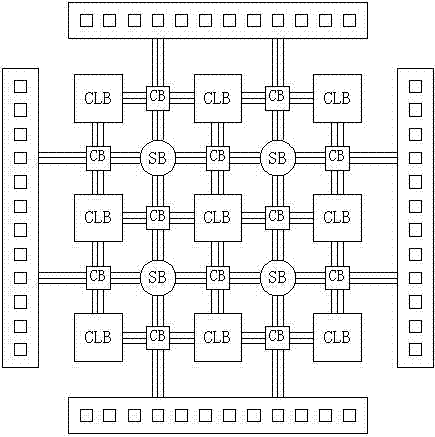

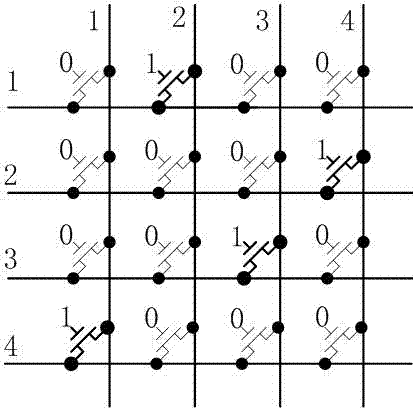

[0061] Traditional FPGA interconnection resources are composed of CB and SB, in which the horizontal and vertical wiring channels are connected through the switch box SB, and the input and output of CLB are connected with each wiring channel through the connection box CB. Both CB and SB in the traditional FPGA structure adopt a space switching structure, and the control switches are composed of transmission tubes or MUX (multiplexer) composed of transmission tubes, such as Figure 8 shown.

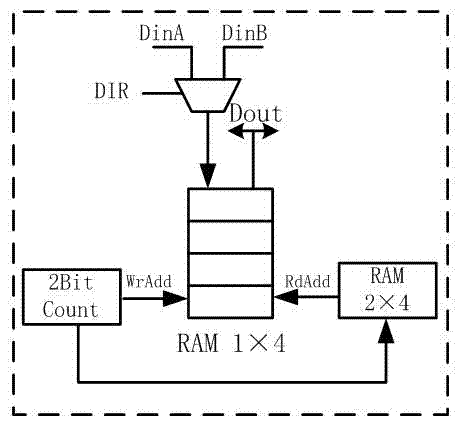

[0062] The invention converts the interconnected parallel signals in the FPGA into serial signals, which can reduce the quantity and area of interconnected resources i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More