BIOS (Basic Input Output System) debugger and debugging method

A debugging method and a debugger technology, which are applied in the detection of faulty computer hardware, etc., can solve the problems of inconvenient testing, increased programming time, time wasting, etc., and achieve the effect of high speed and low testing cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

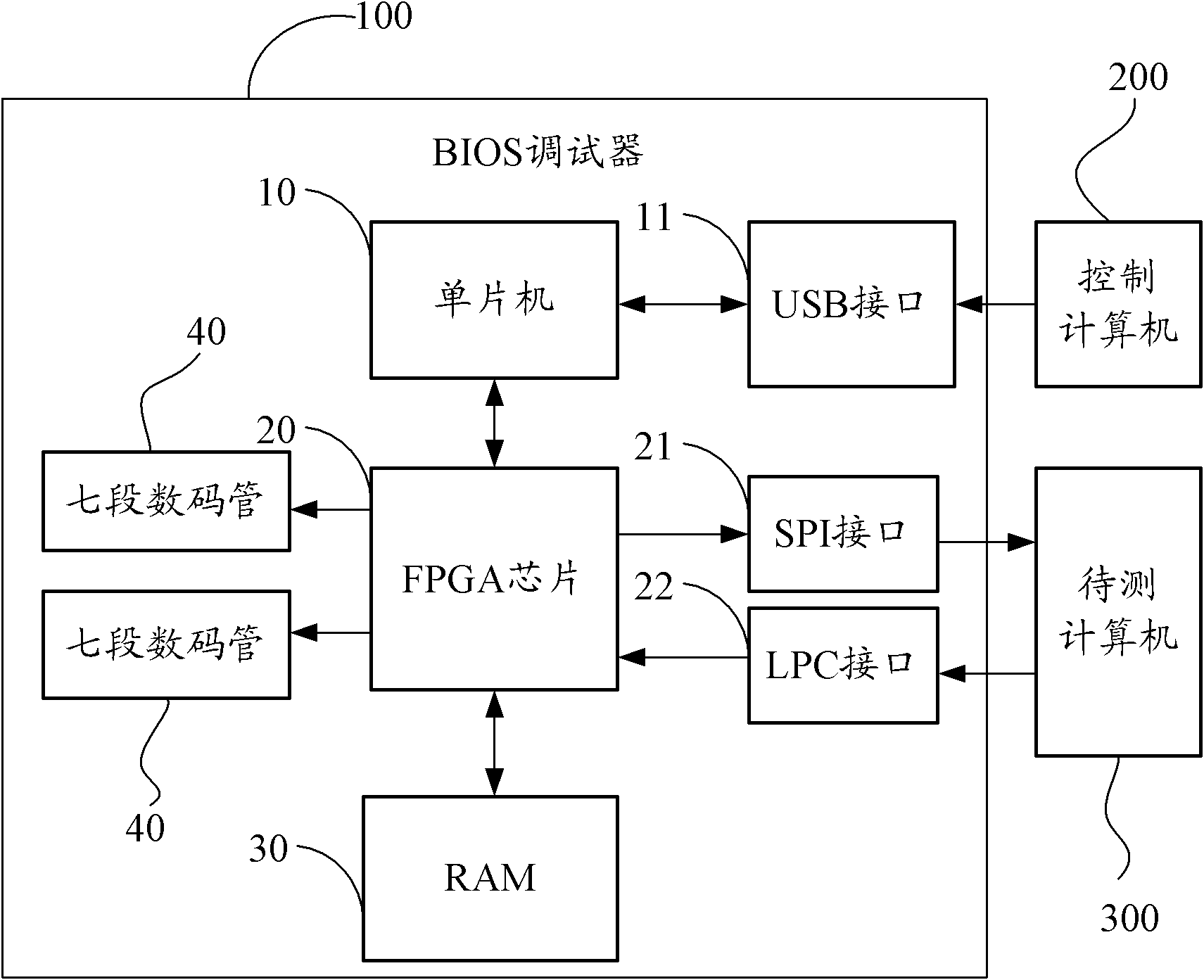

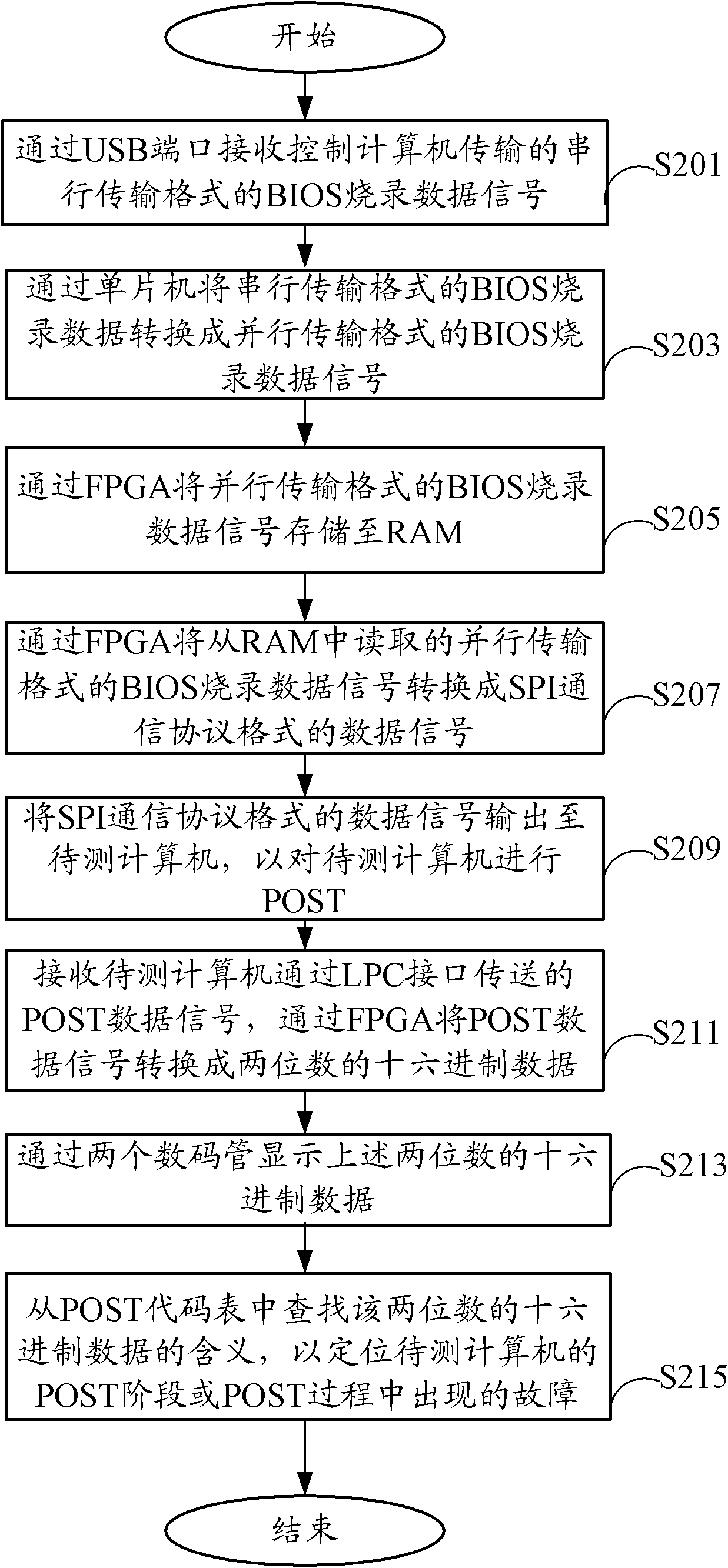

[0012] refer to figure 1 Shown is a functional block diagram of a preferred embodiment of a basic input / output system (BIOS) debugger of the present invention. The BIOS debugger 100 includes a microcontroller 10 , a field-programmable gate array (FPGA) chip 20 , a random access memory (random access memory, RAM) 30 and two seven-segment LEDs 40 . FPGA chip 20 is connected with single-chip microcomputer 10 , RAM 30 and two seven-segment digital tubes 40 . The single-chip microcomputer 10 is connected to the control computer 200 through a universal serial bus (USB) interface 11 , and receives the BIOS programming data signal output by the control computer 200 in a serial transmission format through the USB interface 11 . Afterwards, the microcontroller 10 converts the BIOS programming data signal in the serial transmission format into a BIOS programming data signal in the parallel transmission format to increase the data transmission rate, and outputs the BIOS programming data ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More