Alignment marking method in DMOS (Double-diffusion Metal Oxide Semiconductor) process flow

A technology of alignment marking and process flow, applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve problems such as temperature must be increased, production line equipment program configuration is complicated, and the surface of the wafer is rough, etc., to ensure normal counterpoint effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

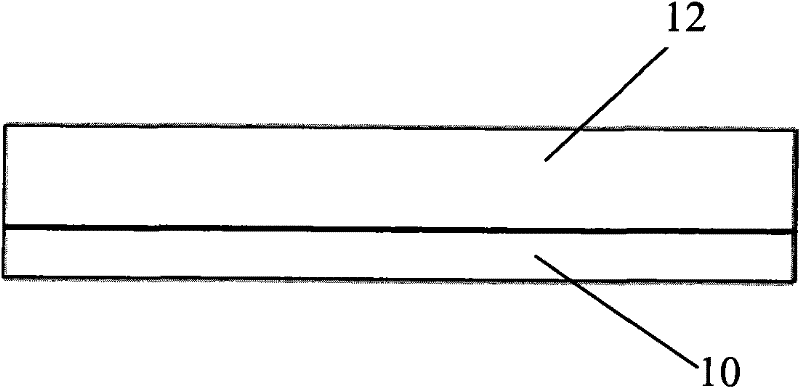

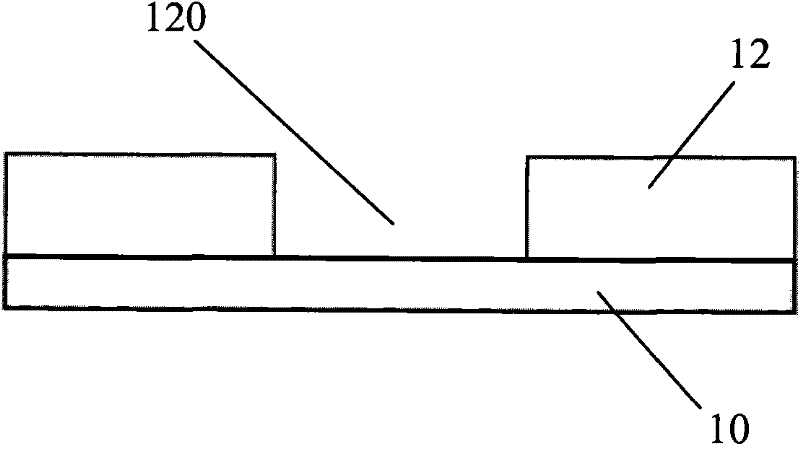

[0019] The implementation process and essential content of the present invention will be described below with preferred embodiments with reference to the accompanying drawings.

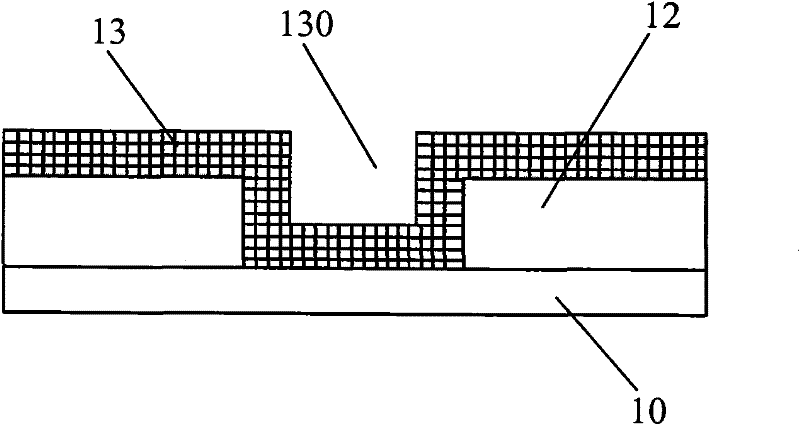

[0020] Such as Image 6 As shown, there is an inorganic membrane structure 101 above the wafer base 100, and the inorganic membrane structure 101 forms a groove 102 after groove etching, and the groove 102 is the most important and basic first alignment for other subsequent processes. mark. The first alignment mark 102 must be concave, and the width must be large enough, otherwise it is easy to be filled with polysilicon and tungsten in the subsequent process engineering. After considering the filling factor, the mark width of the first alignment mark 102 is generally designed to be 4-6 microns.

[0021] Such as Figure 7 with Figure 8 As shown, after the trench 102 is formed, the polysilicon 200 filling begins to form the trench gate. The polysilicon 200 begins to fill both sides of the trench ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com