CMOS (complementary metal-oxide-semiconductor transistor) image sensor for realizing two-dimensional discrete cosine transformation

A two-dimensional discrete cosine, image sensor technology, applied in image communication, color TV parts, TV system parts and other directions, can solve the problem of low acquisition and processing efficiency, increase image sensor power consumption and chip area, restrict image sensor application and other issues to achieve the effect of shortening computing time, reducing parts, and reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

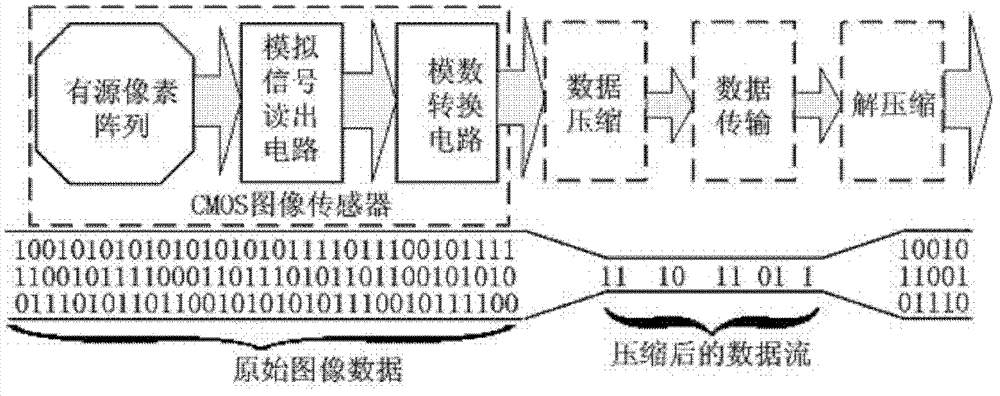

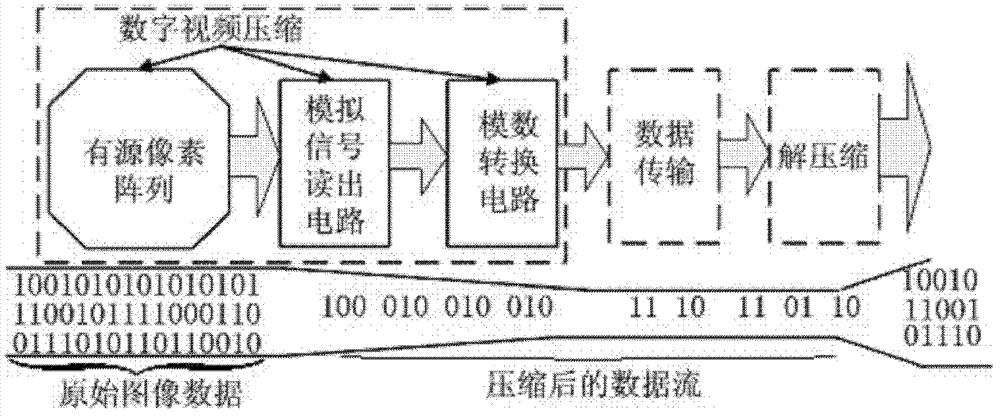

[0031]The traditional CMOS image sensor array architecture includes a pixel array for receiving light signals and converting them into voltage signals, amplifying the voltage signals and performing correlated double sampling (CDS) to eliminate fixed pattern noise (FPN) and reset noise readout circuit, a multiplexer (MUX) for selecting specific pixel values for subsequent amplification, a programmable gain amplifier (DPGA) for amplifying voltage signals corresponding to pixel values for analog-to-digital conversion, and converting voltage values into digital The signal is processed by an analog-to-digital converter (ADC) for subsequent digital image processing and peripheral control timing circuits. This invention will improve the traditional CMOS image sensor architecture and realize 2D-DCT by mixed signal processing.

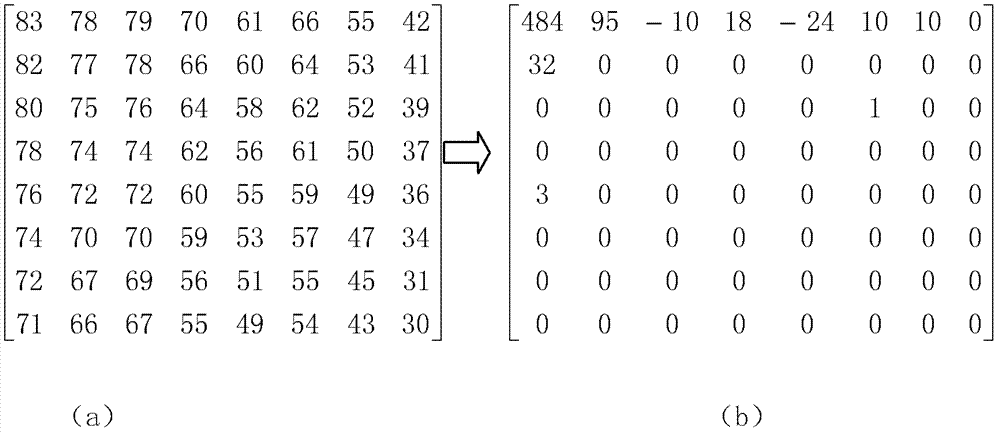

[0032] Suppose {X(m, n)|m=0, 1,..., M-1; n=0, 1,..., N-1} is a two-dimensional image signal data matrix, and its two-dimensional discrete cosine Transfo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More