Junctionless silicon nanowire transistor based on bulk-silicon material and method for manufacturing junctionless silicon nanowire transistor

A silicon nanowire and silicon material technology is applied in the field of junction-free silicon nanowire transistors and their preparation to achieve the effects of realizing source-drain contact resistance, realizing integration, and small source-drain contact resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

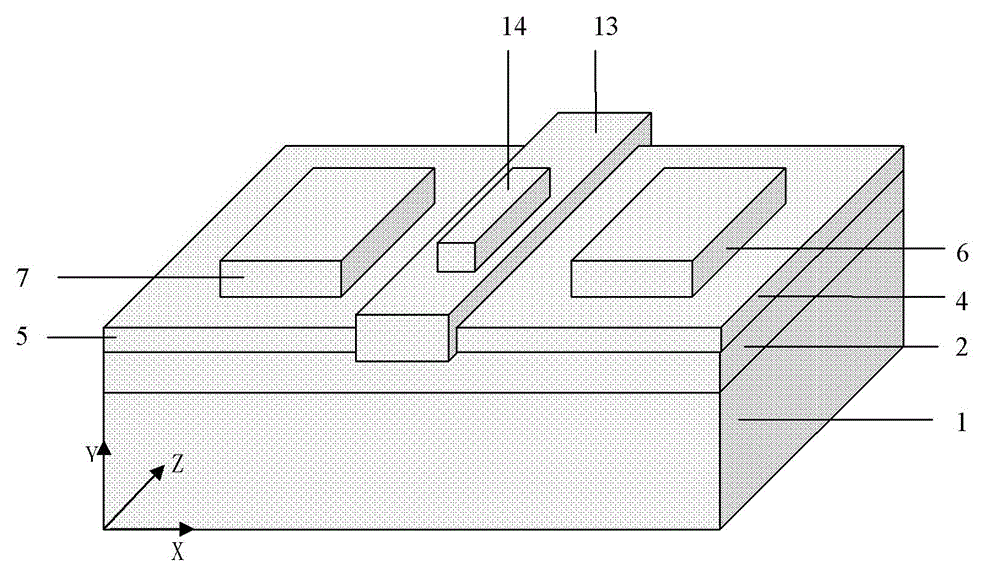

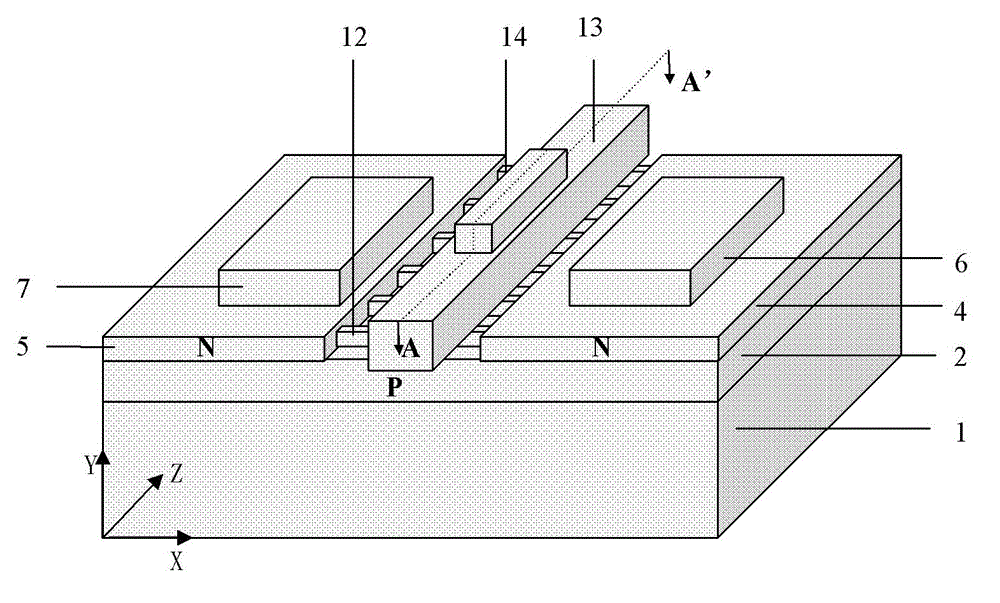

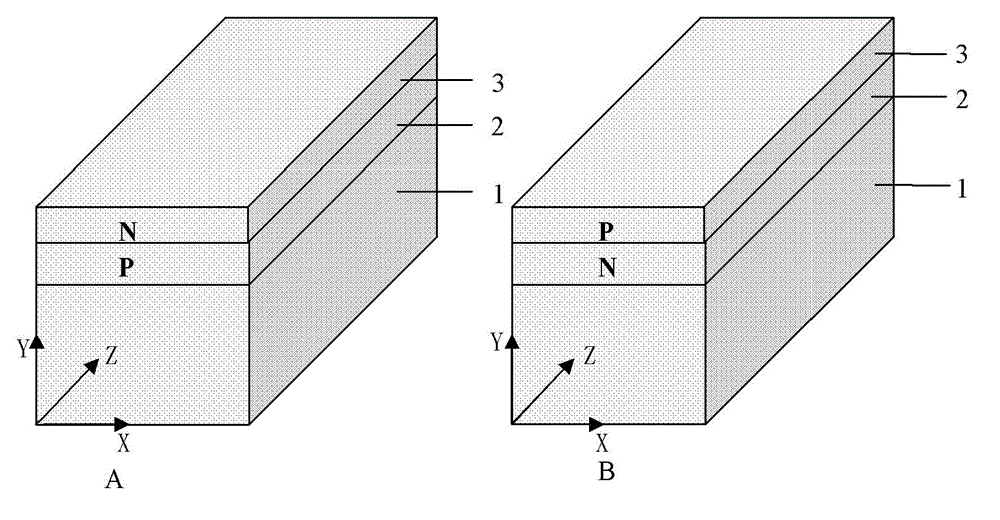

[0046] see Figure 1 to Figure 6 As shown, the junction-free silicon nanowire transistor based on bulk silicon material provided by the present invention includes: an integral silicon substrate 1; a first doped layer 2, which is formed on the bulk silicon by ion implantation The upper part of the substrate 1, and the doping type of the first doped layer 2 is P-type or N-type; a second doped layer 3, the second doped layer 3 is formed on the bulk silicon substrate by ion implantation 1, and located on the first doped layer 2, the doping type of the second doped layer 3 is opposite to that of the first doped layer 2, and different types of doped layers form a PN junction Play the role of electrical isolation; a source regi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More