TSV front end portion interconnection process

A process and substrate surface technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of large film stress, increased process difficulty, easy delamination or cracks between the insulating layer and the substrate, and achieve improved quality and Reliability, the effect of reducing difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The present invention reduces or removes the stress concentration area of the TSV conductive column, reduces the possibility of delamination or cracks between the insulating layer and the substrate due to stress; It will highlight the defects of this existing process and realize the interconnection between the TSV conductive pillar and the redistribution layer metal.

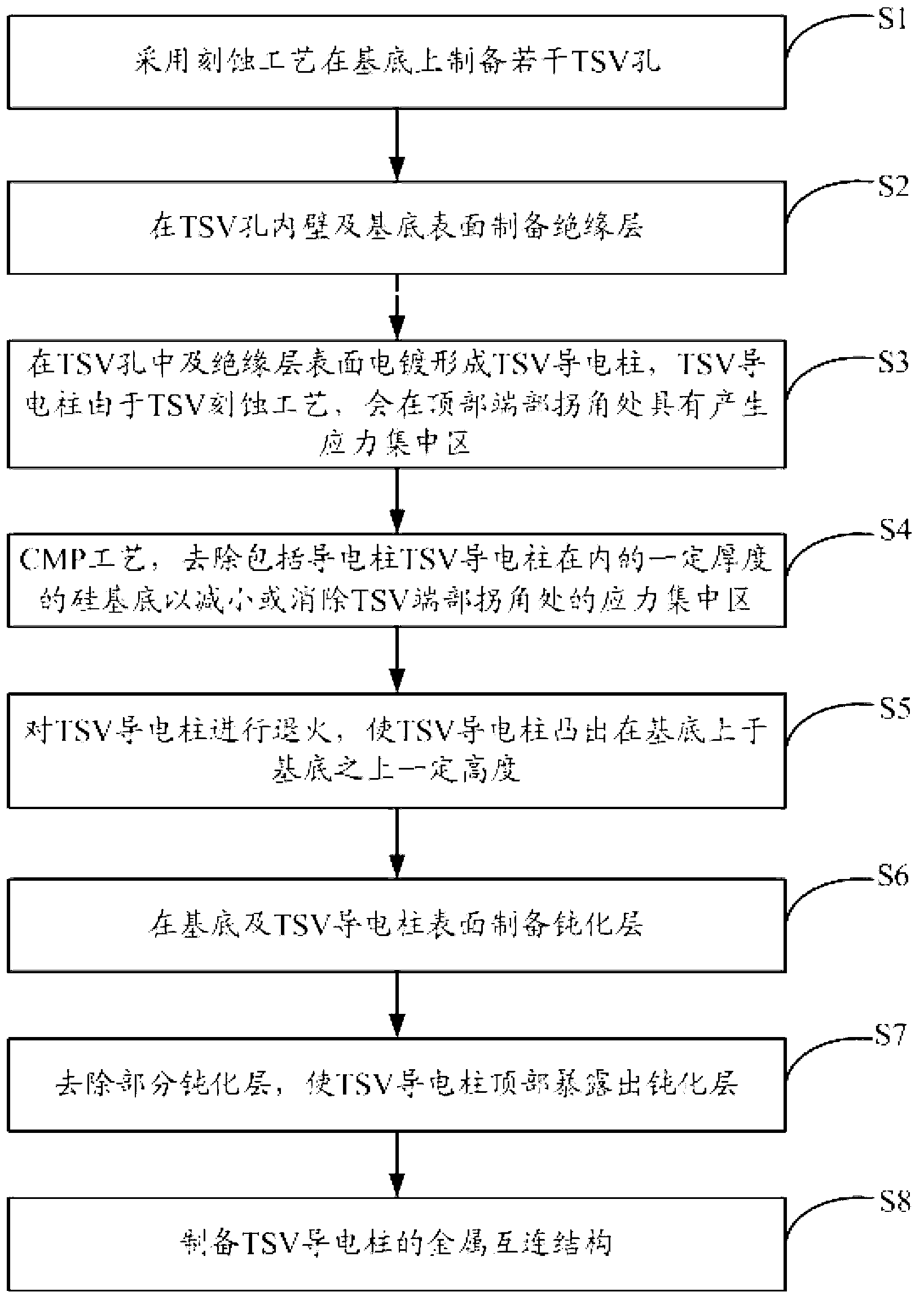

[0038] Specifically, such as figure 1 As shown, a TSV front end interconnection process disclosed in the present invention includes the following steps:

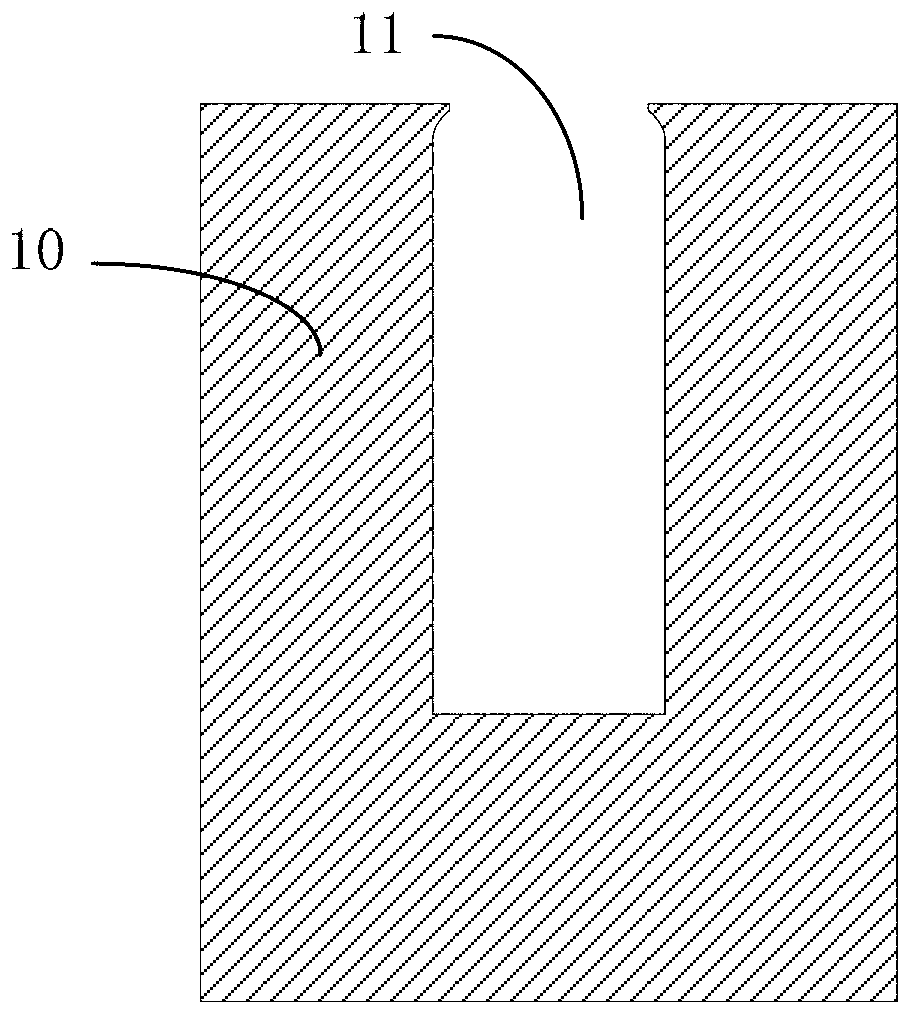

[0039] S1, using an etching process to prepare a number of TSV holes on the substrate;

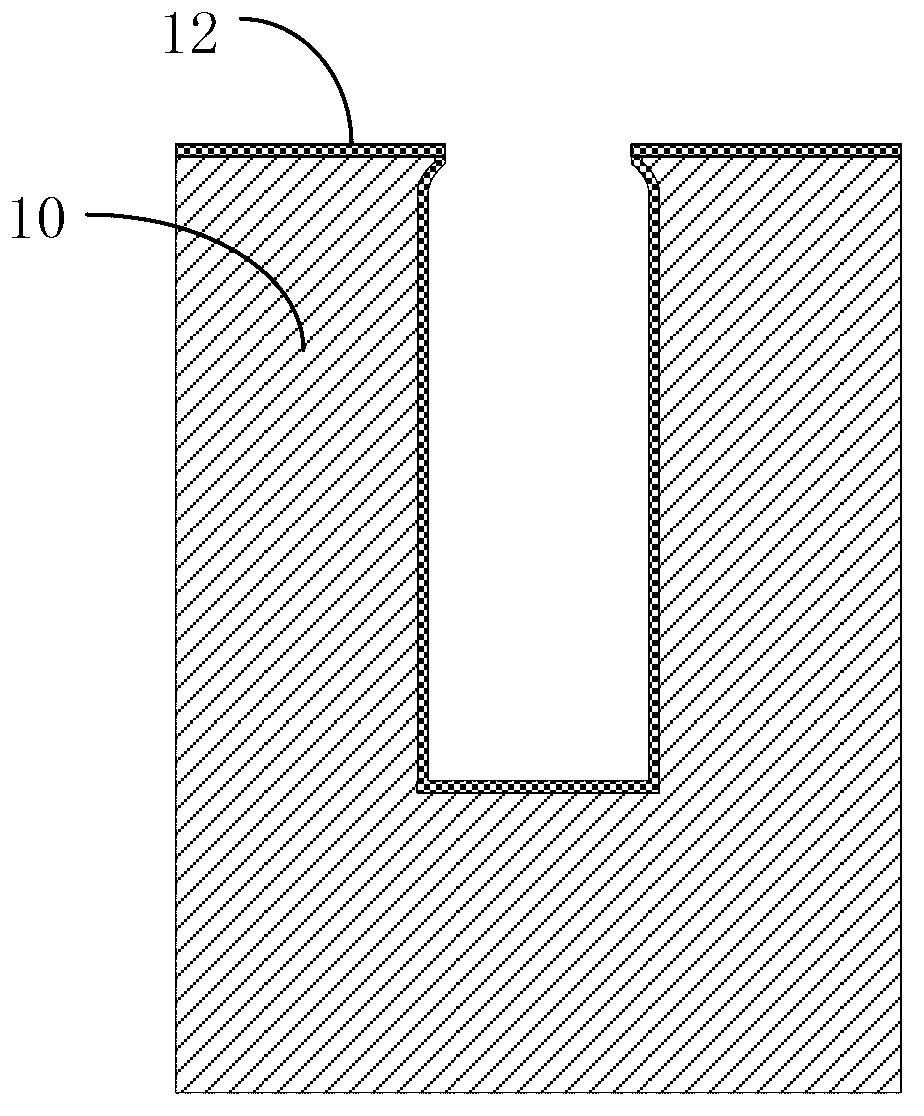

[0040] S2, preparing an insulating layer on the inner wall of the TSV hole and the surface of the substrate;

[0041] S3, forming TSV conductive columns in the TSV holes and on the surface of the insulating layer by electroplating, and the TSV conductive columns will generate stress concentration areas at the corners of the ends due to the TSV etching process; ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com