Manufacturing method of multi-wavelength laser array chip

A technology of multi-wavelength lasers and array chips, applied in the direction of laser devices, semiconductor laser devices, optical waveguide semiconductor structures, etc., can solve the problems of high device manufacturing costs, difficulty in mass production and application, and high cost of electron beam exposure technology. Achieve the effect of low-loss multi-wavelength emission

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

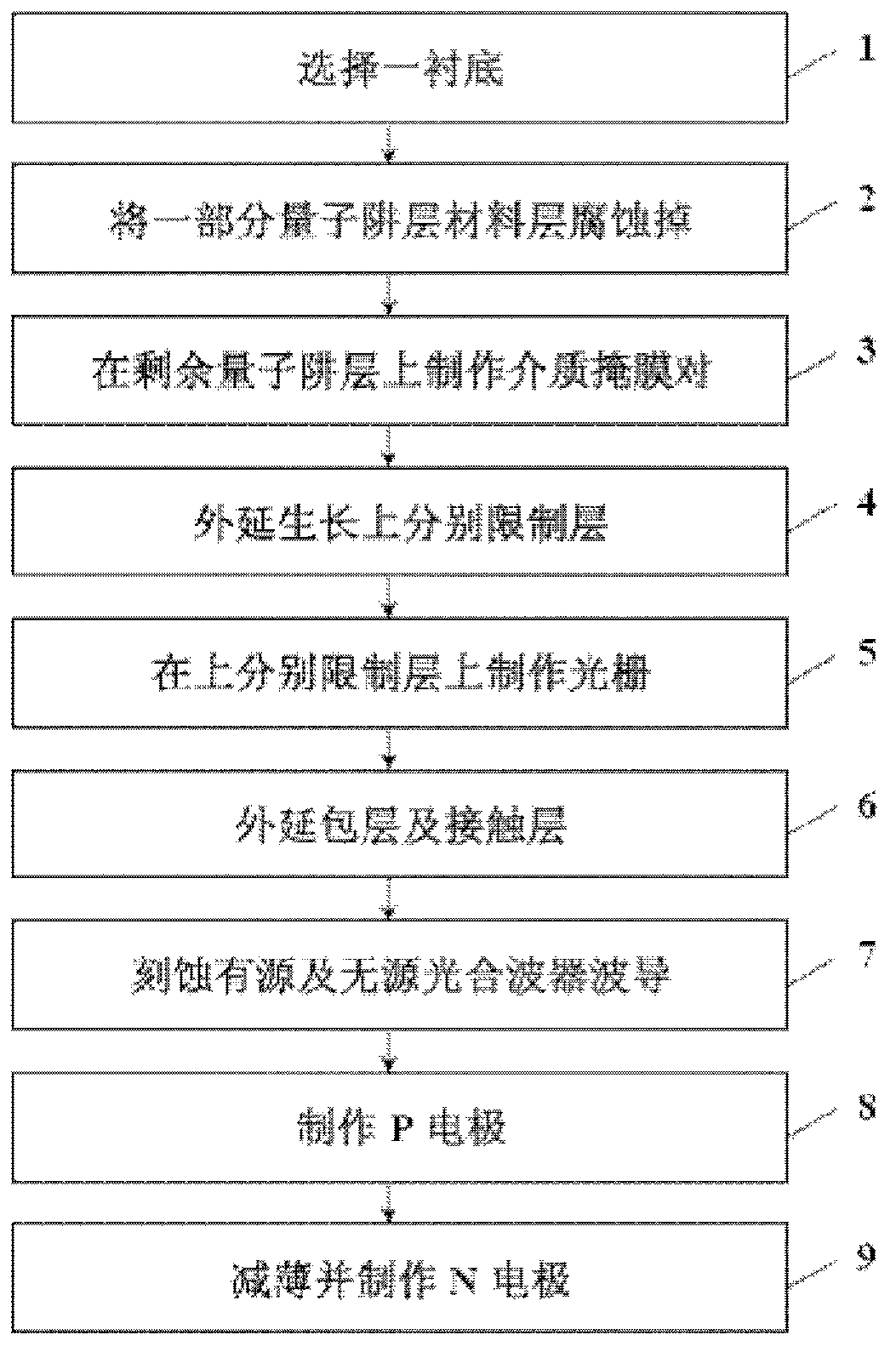

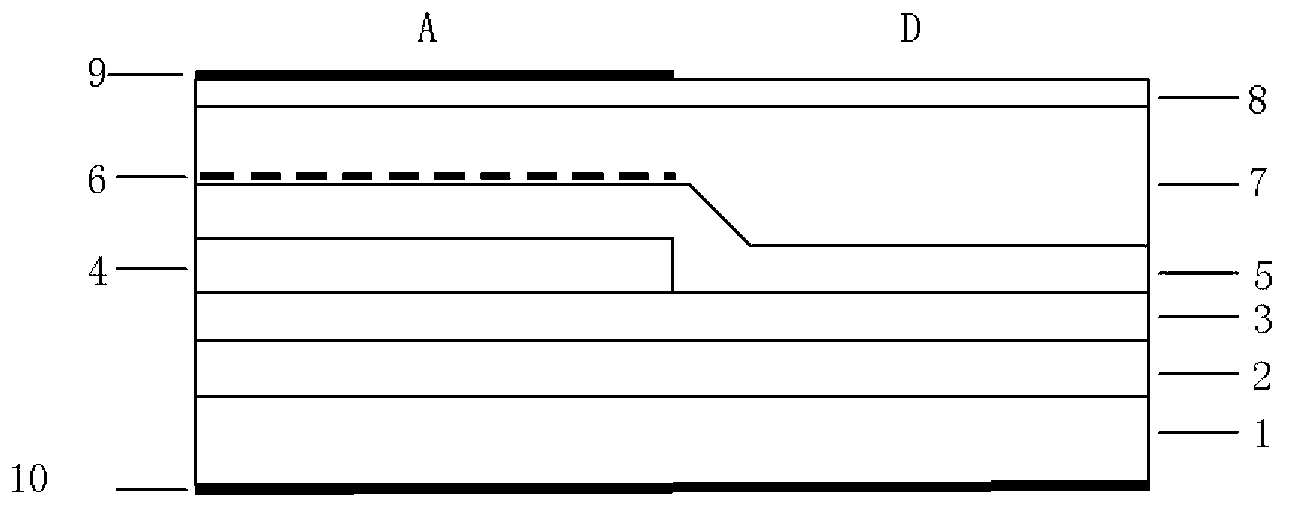

[0037] see figure 1 and Figure 3 to Figure 8 As shown, the present invention provides a method for manufacturing a multi-wavelength laser array chip, comprising the steps of:

[0038] Step 1: growing a buffer layer 2 , a lower confinement layer 3 and a multiple quantum well layer 4 on a substrate 1 . The material of the substrate 1 is GaAs, InP, GaN, SiC or Si.

[0039] Step 2: Etching a part of the multi-quantum well layer 4, the etched part is the passive optical combiner region D, and the remaining part is the active region A;

[0040] Step 3: making a dielectric mask pair Ma( Figure 7 ) or Mb( Figure 8 ). Dielectric mask pair patterns appear in pairs at the interval of array unit s, and for mask pattern Ma( Figure 7 ) in which the distance between the mask pairs remains constant, and the mask width increases gradually, that is, the widths of the masks M1, M2, M3 to MN satisfy W1 Figure 8 ) in which the mask width is constant and the distance between mask pairs is...

Embodiment 2

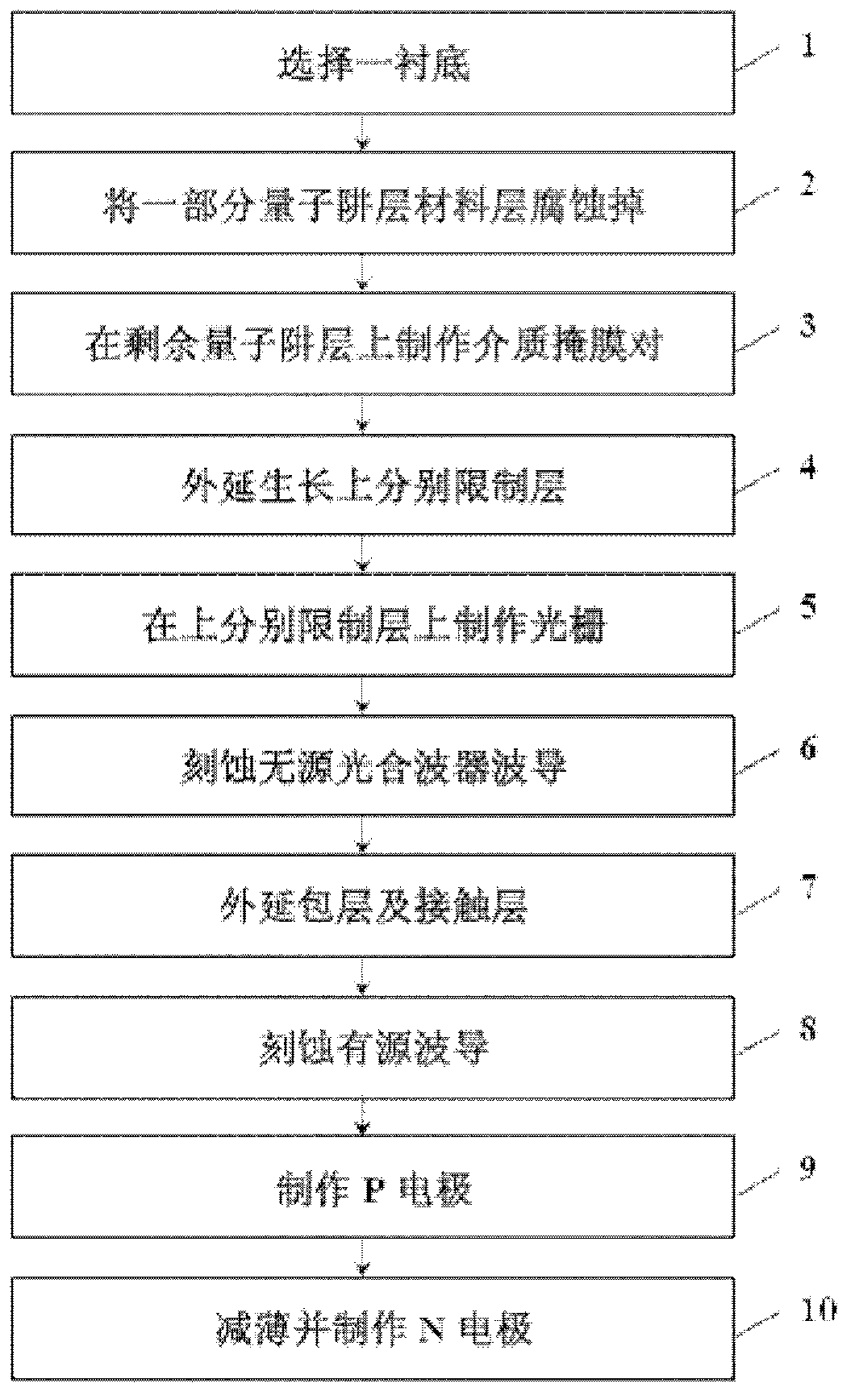

[0051] see again Figure 2 to Figure 8 As shown, the present invention provides a method for manufacturing a multi-wavelength laser array chip, comprising the steps of:

[0052] Step 1: growing a buffer layer 2 , a lower confinement layer 3 and a multiple quantum well layer 4 on a substrate 1 . The material of the substrate 1 is GaAs, InP, GaN, SiC or Si;

[0053] Step 2: Etching a part of the multi-quantum well layer 4, the etched part is the passive optical combiner region D, and the remaining part is the active region A;

[0054] Step 3: making a dielectric mask pair Ma( Figure 7 ) or Mb( Figure 8 ). Dielectric mask pair patterns appear in pairs at the interval of array unit s, and for mask pattern Ma( Figure 7 ) in which the distance between the mask pairs remains constant, and the mask width increases gradually, that is, the widths of the masks M1, M2, M3 to MN satisfy W1 Figure 8 ) in which the mask width is constant and the distance between mask pairs is gradual...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More