Graphene Enhanced Ingaas Infrared Detector

An infrared detector, graphene technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of difficulty in further improving mobility, affecting efficient absorption and conversion, and difficulty in growing InP single crystals, so as to improve photoelectric conversion efficiency. , the effect of low defect density and high relaxation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

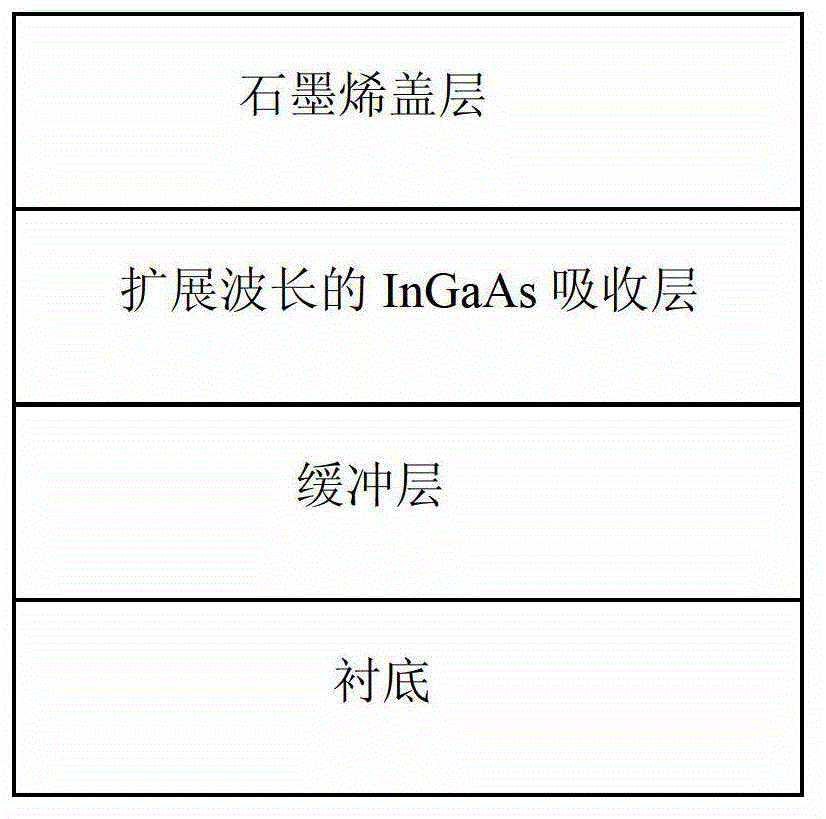

[0024] The structure of a graphene-enhanced InGaAs infrared detector with a cutoff wavelength of 2.6 μm is as follows: a thickness of about 1 μm is sequentially grown on an n-type GaAs substrate, and the Si doping concentration is 2×10 18 cm -3 n-type InAs 0.60 P 0.40 Buffer layer, continue to grow to a thickness of 2.5 μm, and a Si doping concentration of 8×10 16 cm -3 (lowly doped) n-type In 0.82 Ga 0.18 As absorption layer, and finally a single-layer p-type graphene cap layer is grown to form a pin detector structure.

[0025] In this embodiment, firstly, S-doped n-type GaAs is used as the substrate, and Si-doped InAs is grown on the GaAs substrate by the MOCVD system using a two-step method. 0.60 P 0.40 Buffer layer, first grow a layer of InAs with a thickness of about 100nm at a temperature of 450°C 0.60 P 0.40 , and then raise the temperature to 580°C, during the temperature rise process the buffer layer InAs 0.60 P 0.40 Anneal and recrystallize to release the...

specific Embodiment approach 2

[0026] A graphene-enhanced InGaAs infrared detector structure with a cutoff wavelength of 2.6 μm is: sequentially grown on an n-type InP substrate with a thickness of about 2 μm and a Si doping concentration of 2×10 18 cm -3 n-type In 0.82 al 0.18 As buffer layer, continue to grow to a thickness of 3.5 μm, and a Si doping concentration of 8×10 16 cm -3 (lowly doped) n-type In 0.82 Ga 0.18 As absorption layer, and finally grow multi-layer p-type graphene capping layer to form pin detector structure.

[0027]In this embodiment, firstly, S-doped n-type InP is used as the substrate, and Si-doped In is grown on the InP substrate by the MOCVD system using a two-step method. 0.82 al 0.18 As buffer layer, first grow a layer of about 200nm In at a temperature of 450°C 0.82 al 0.18 As, then raise the temperature to 580°C, the buffer layer In during the heating process 0.82 al 0.18 As is annealed and recrystallized to release the stress caused by the lattice mismatch and becom...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More