Flexible ZnO based thin film transistor and preparation method thereof

A technology of thin film transistors and flexible substrates, applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of not using photolithographic patterns, poor surface flatness, not using panels, etc., to enhance operability and use Reliability, enhanced water and oxygen barrier properties, improved operability and stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

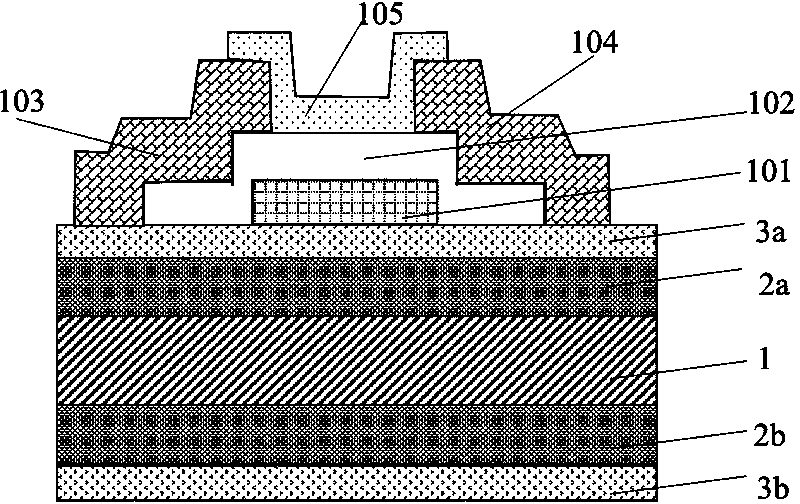

[0046] Such as figure 1 As shown, the manufacturing process of the bottom gate of the present invention, the bottom contact zinc oxide thin film transistor comprises the following steps:

[0047] a) Pretreatment of flexible substrates;

[0048] b) Depositing a gate electrode film (101) by a Lift-off process;

[0049] c) depositing gate insulating material (102);

[0050] d) forming a gate insulating layer pattern by photolithography;

[0051] e) Depositing source and drain electrodes (103, 104) by Lift-off process;

[0052] f) spin-coating an inorganic solution to obtain a ZnO semiconductor layer (105);

[0053] g) Obtain the channel region pattern by photolithographic wet etching.

[0054] In step a), the pretreatment of the flexible substrate is the same as above.

[0055] The lift-off process in the step b) is specifically, using Ruihong positive resist, spin-coating at 5000rpm for 30s, pre-baking at 95°C for 10min, exposing for 40s, developing for 20-40s, and post-ba...

Embodiment 2

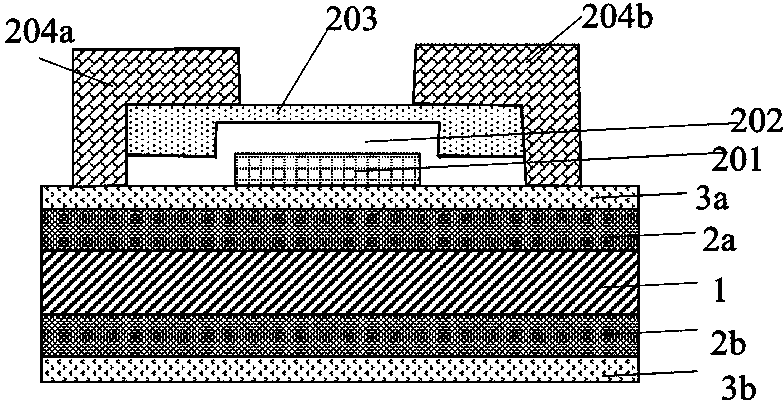

[0076] Preparation method of bottom gate and top contact TFT: 1, substrate pretreatment; 2, depositing gate electrode 201; 3, depositing gate insulating layer 202; 4, depositing ZnO semiconductor channel layer 203; 5, depositing Product source and drain (204a, 204b). In this method, the gate insulating layer and the channel layer can be etched simultaneously with a set of photolithography plates to form patterns, and the gate electrode, source and drain electrodes are made by Lift-off process, and this structure can avoid the influence of the annealing process on the source and drain electrodes.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More