0.1-5GHz CMOS (complementary metal oxide semiconductor) power amplifier

A power amplifier and power amplifier circuit technology, applied in the field of ultra-wideband CMOS RF power amplifiers, can solve the problems of limiting the power capacity of a single transistor, limiting the output voltage swing of the transistor drain, and increasing difficulties, so as to avoid low breakdown voltage characteristics, improved input circuit matching, and improved stability and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

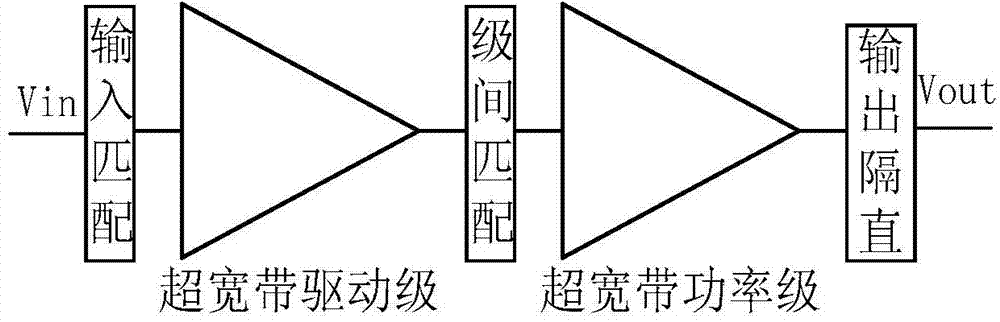

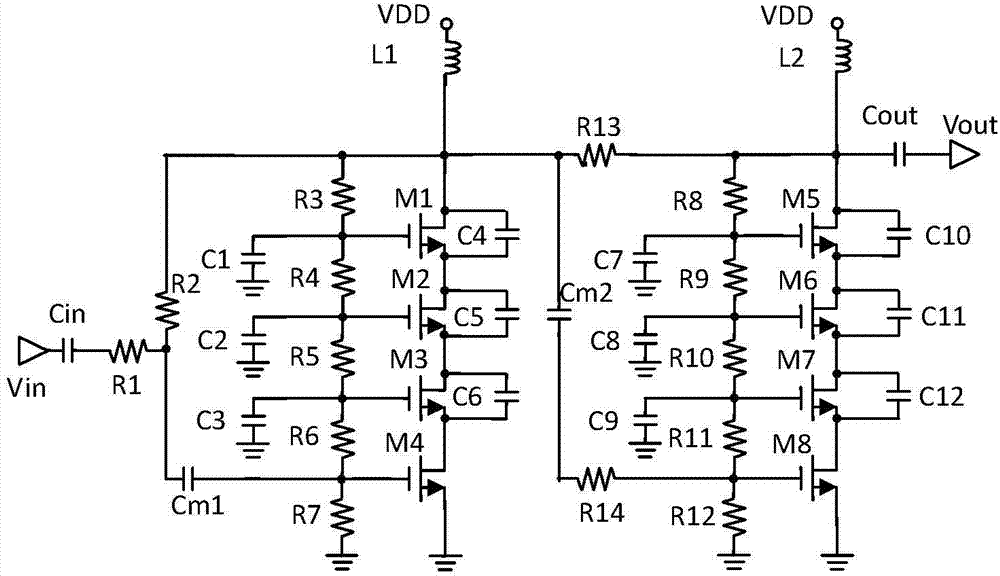

[0028] Such as figure 1 As shown, the 0.1-5GHz ultra-wideband CMOS power amplifier of the present invention is an ultra-wideband radio frequency power amplifier with a two-stage common-source four-times series distributed structure, which is designed using a CMOS process.

[0029] The amplifier includes an input matching circuit, an ultra-wideband driving stage amplifying circuit, an ultra-wideband power amplifying circuit and an output DC blocking circuit, wherein the ultra-wideband driving stage amplifying circuit as the first stage is used to realize the ultra-wideband driving power gain of the amplifier, and Ensure that the ultra-wideband S11 parameter matching of the entire circuit; the ultra-wideband power output stage circuit as the second stage is used to ensure the ultra-wideband power output of the entire circuit and a good ultra-wideband S22 parameter matching, the ultra-wideband drive stage amplifier circuit and the ultra-wideband The broadband power amplifying cir...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More