Method for improving silicon chip warping degree

A warpage, silicon wafer technology, used in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., to solve problems such as debris and constant silicon wafer alarms

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] see Figure 7 As shown, in the following embodiments, the method for improving the warpage of silicon wafers includes the following steps:

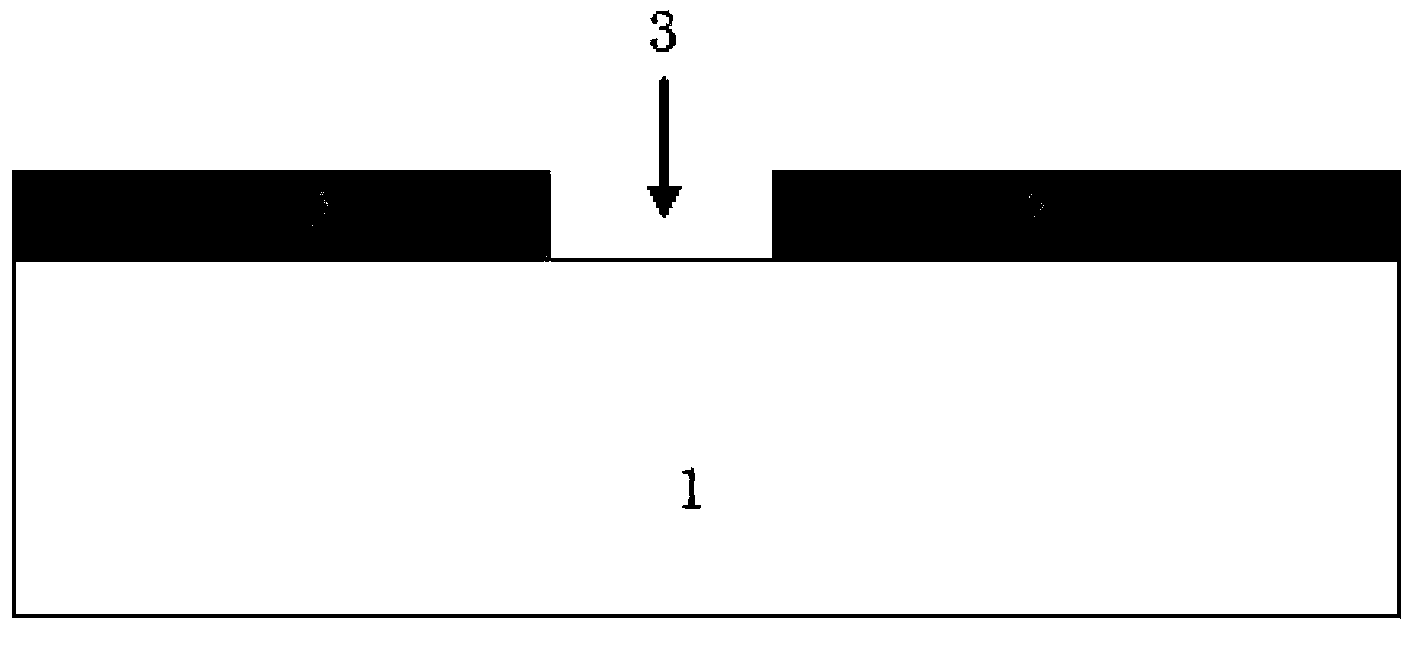

[0024] Step 1. Combine figure 1 As shown, a pre-metal dielectric layer 2 is formed on a silicon substrate 1 , and a contact hole 3 penetrating through the pre-metal dielectric layer 2 is formed in the pre-metal dielectric layer 2 .

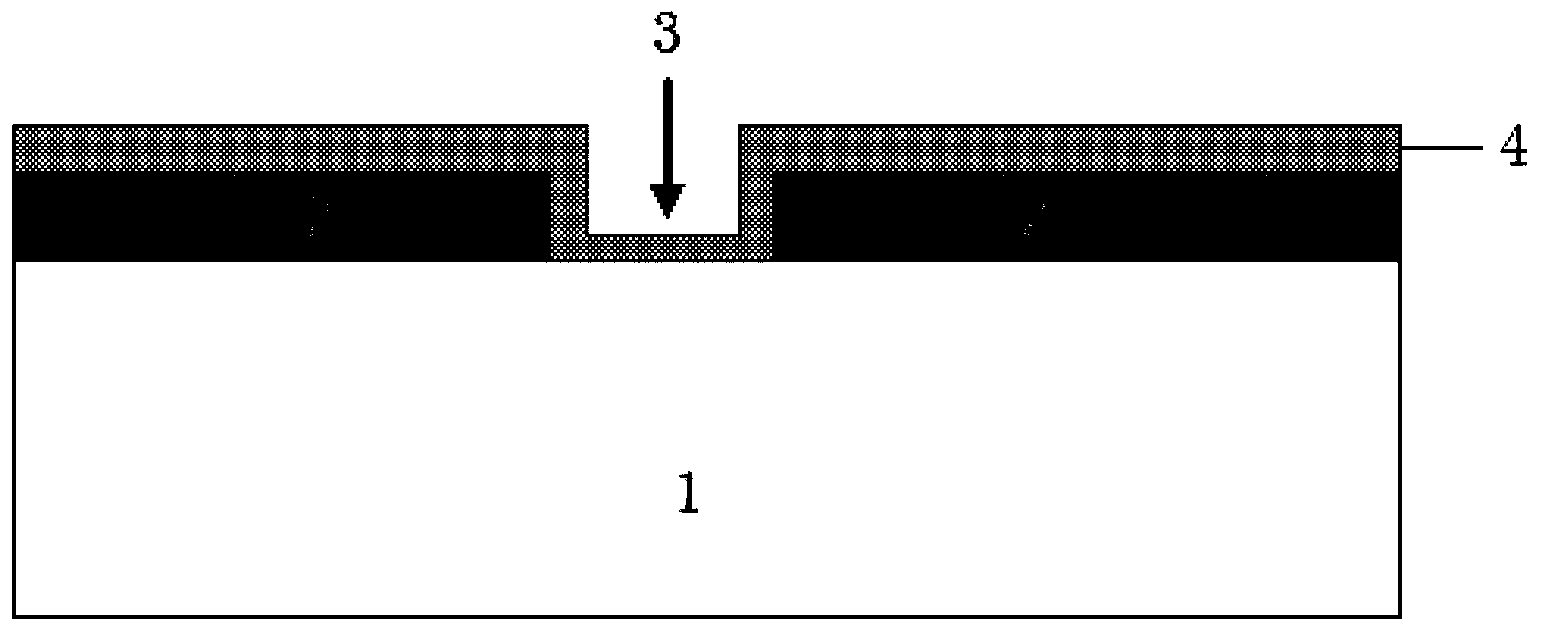

[0025] Step two, combine figure 2 As shown, a metal connection layer 4 is deposited on the pre-metal dielectric layer 2 and in the contact hole 3 . The deposited metal connection layer 4 includes but not limited to titanium, cobalt, tantalum; the thickness of the metal connection layer 4 is The deposition method of the metal connection layer 4 includes but not limited to chemical vapor deposition (CVD) and sputtering.

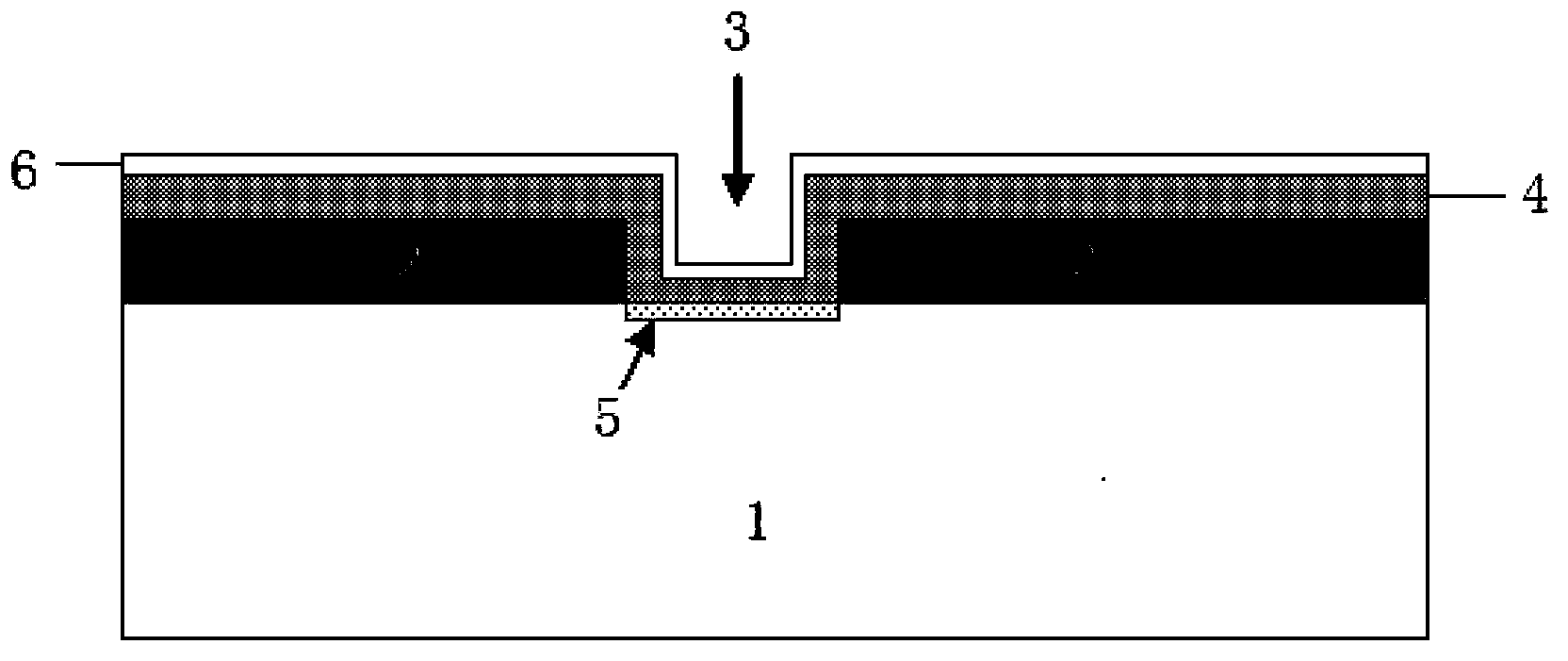

[0026] Step three, combine image 3 As shown, the metal connection layer 4 is subjected to rapid thermal annealing treatment. After the thermal annealing treatment, a metal silic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More