A method of manufacturing a fin field effect transistor

A field effect transistor and fin technology, which is applied in the field of fin field effect transistor preparation, can solve the problems of difficulty in controlling the height of the fin, affecting the performance of the fin field effect transistor, etc., and achieves easy control of the aspect ratio of the fin and easy height difference. The effect of controlling and improving yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

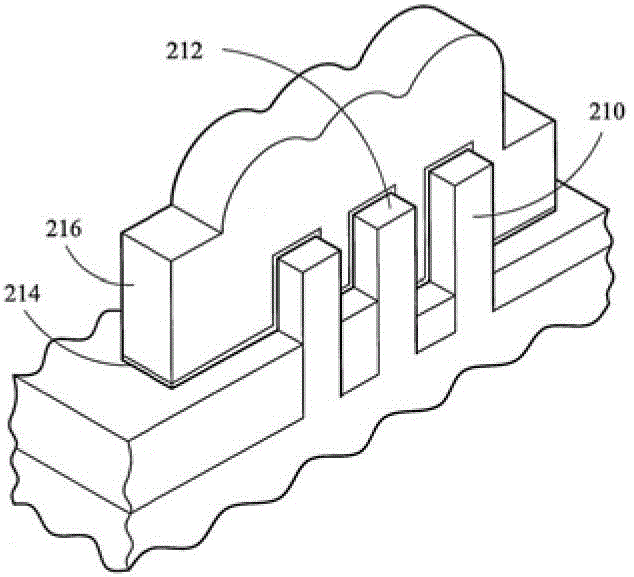

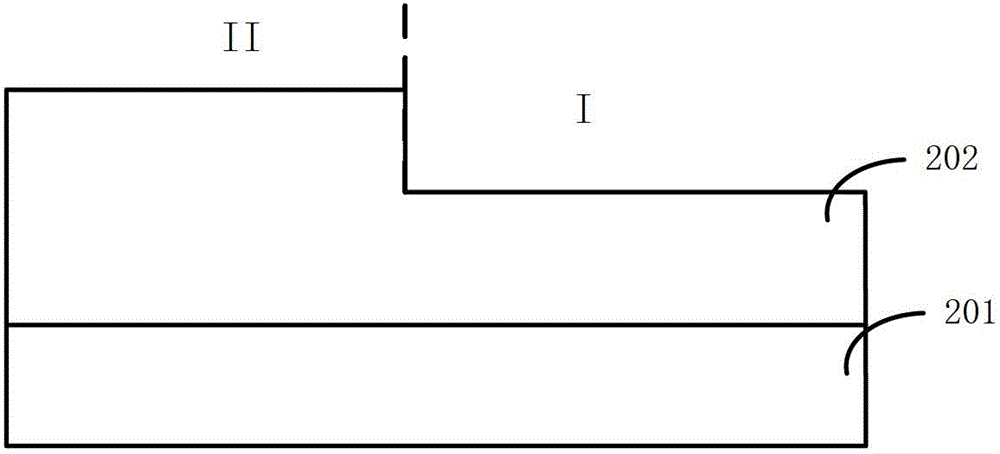

[0040] According to the flow chart, the present invention can have the following two implementations, which will be described separately below, first referring to Figure 2-7 Explain the first case:

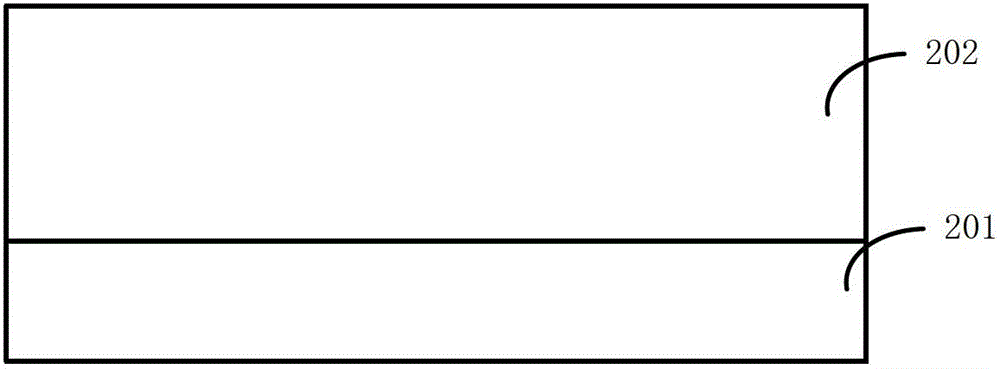

[0041] refer to figure 2 Firstly, a semiconductor substrate 201 is provided, and the semiconductor substrate may be at least one of the materials mentioned below: silicon, Ge or SiGe and the like.

[0042]An isolation structure may also be formed in the semiconductor substrate, and the isolation structure is a shallow trench isolation (STI) structure or a local oxide of silicon (LOCOS) isolation structure. In the present invention, shallow trench isolation is preferably formed, and various well structures and channel layers on the substrate surface are also formed in the semiconductor substrate. Generally speaking, the conductivity type of ion doping forming the well structure is the same as that of the channel layer, but the concentration is lower than that of the gate channe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More