Semiconductor device and forming method thereof

A semiconductor and device technology, applied in the field of semiconductor devices and their formation, can solve problems such as poor performance, and achieve the effect of saving process time and simplifying process steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

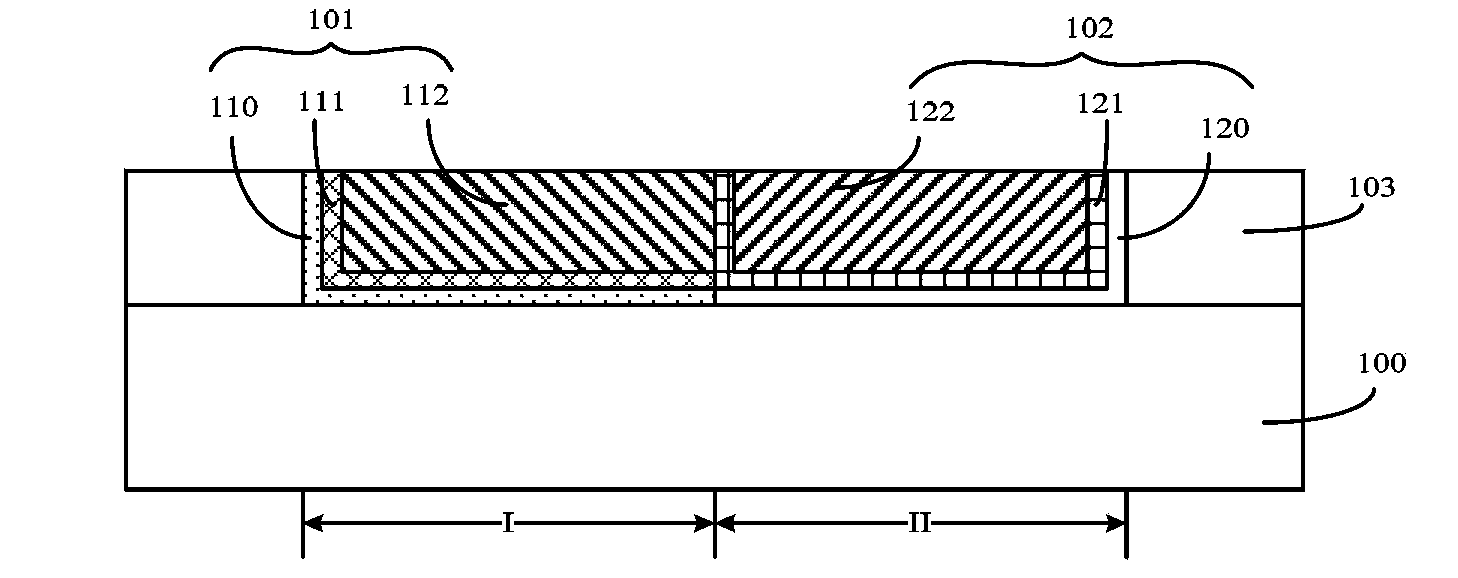

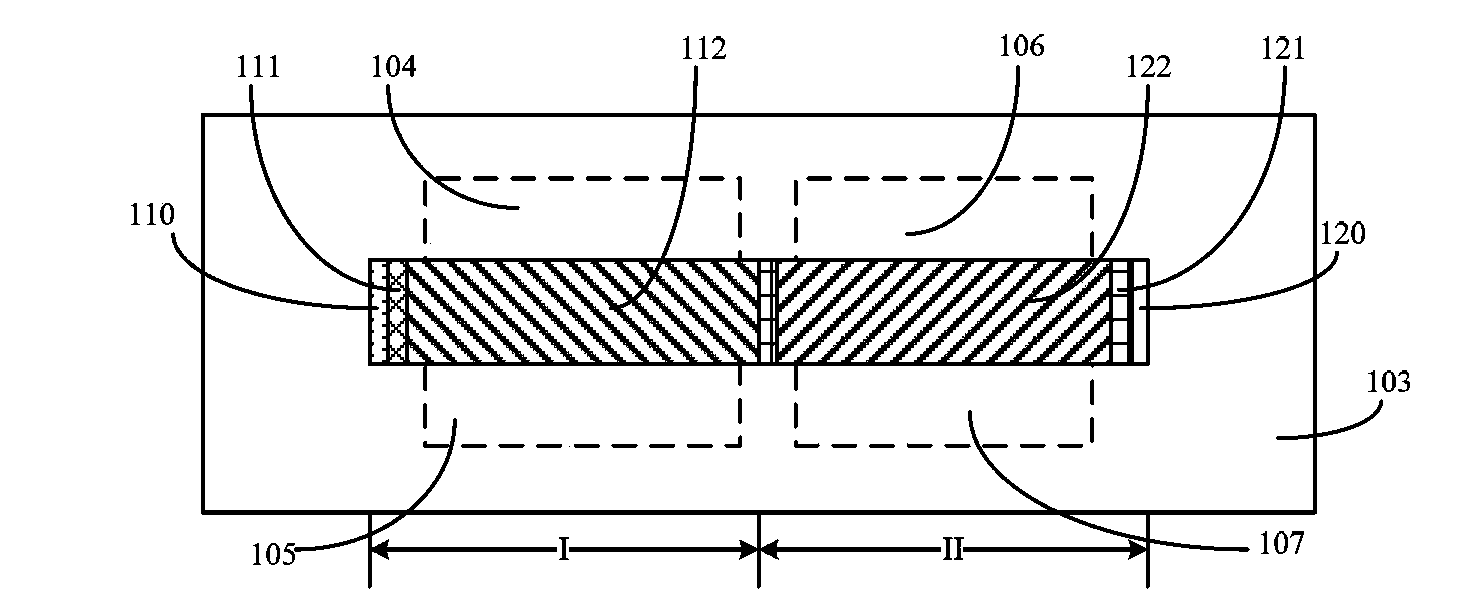

[0032] Figure 6 to Figure 11 It is a schematic cross-sectional structure diagram of the formation process of the semiconductor device described in the first embodiment of the present invention.

[0033] Please refer to Image 6 , provide a semiconductor substrate 300, the semiconductor substrate 300 includes adjacent first region I and second region II; form a dummy gate layer 301 on the surface of the semiconductor substrate 300, and cover the dummy gate layer The first dielectric layer 302 on the sidewall of 301, the dummy gate layer 301 is located on the surface of the semiconductor substrate 300 in the first region I and the second region II, and the surface of the first dielectric layer 302 and the dummy The surface of the gate layer 301 is flush.

[0034] The semiconductor substrate 300 is used to provide a working platform for subsequent processes; the semiconductor substrate 300 is a silicon substrate, a silicon-germanium substrate, a silicon carbide substrate, a si...

no. 2 example

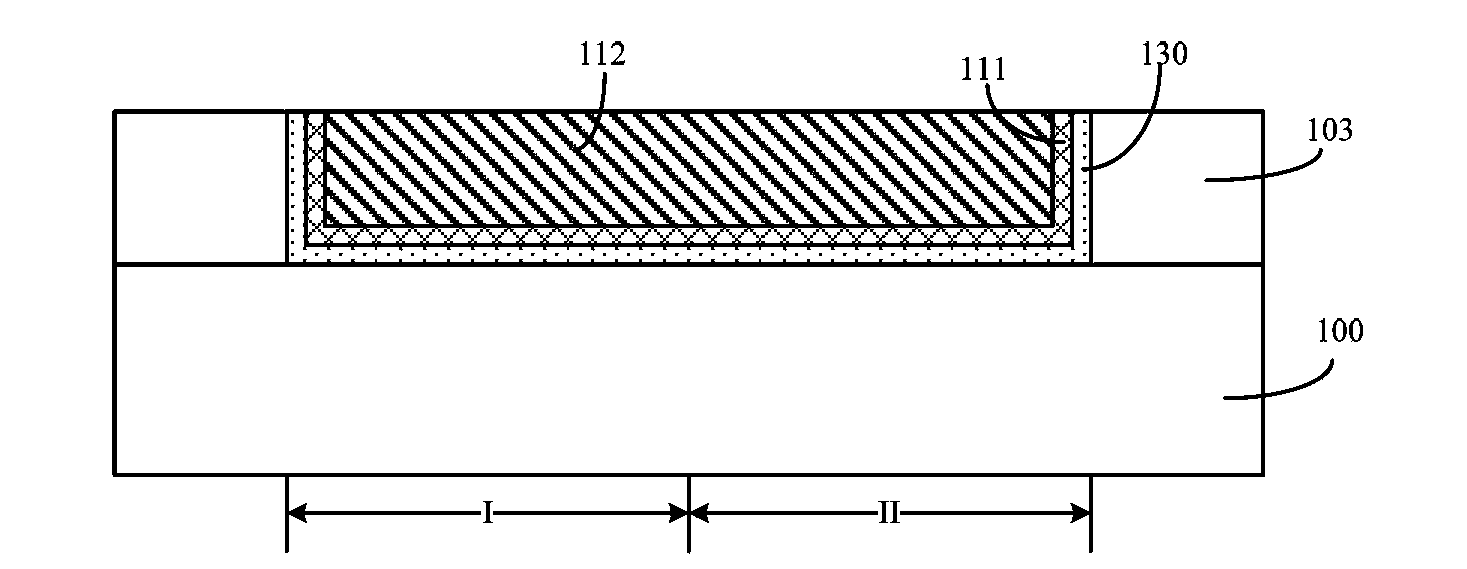

[0073] Figure 12 to Figure 14 It is a schematic cross-sectional structure diagram of the formation process of the semiconductor device described in the second embodiment of the present invention.

[0074] Please refer to Figure 12, provide a semiconductor substrate 200, the semiconductor substrate 200 includes adjacent first region I and second region II; form a dummy gate layer (not shown) on the surface of the semiconductor substrate 200, and cover the The first dielectric layer 202 on the sidewall of the dummy gate layer, the dummy gate layer is located on the surface of the semiconductor substrate 200 in the first region I and the second region II, the surface of the first dielectric layer 202 is in contact with the The surface of the dummy gate layer is flush; the dummy gate layer is removed until the semiconductor substrate 200 is exposed, forming a first opening; forming in the first opening: covering the sidewall and bottom of the first opening The high K dielectri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com