Shallow groove isolation structure forming method

An isolation structure, shallow trench technology, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of easy occurrence of grooves 117, affecting the electrical performance of semiconductor devices, and leakage of semiconductor devices PMOS transistors, etc. The effect of electrical properties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0032] refer to Figure 6 , providing a semiconductor substrate 201, on which a pad oxide layer 203 and a mask layer 205a are sequentially formed from bottom to top.

[0033] In this embodiment, the material of the semiconductor substrate 201 is single crystal silicon or single crystal silicon germanium, or single crystal carbon-doped silicon; or may also include other materials, which are not limited in the present invention.

[0034] The mask layer 205a is a single-layer structure, and the material of the mask layer 205a is silicon nitride or polysilicon.

[0035] The material of the pad oxide layer 203 is silicon oxide, which can be formed by a thermal oxidation process or a chemical vapor deposition process. The pad oxide layer 203 is used to repair defects existing on the surface of the semiconductor substrate 201, improve the degree of bonding between the mask layer 205a and the semiconductor substrate 201, and prevent the mask layer 205a from being well bonded to the s...

no. 2 example

[0055] refer to Figure 12 , providing a semiconductor substrate 301, on which a pad oxide layer 303 and a mask layer 305a are sequentially formed from bottom to top, and an opening 311 exposing the pad oxide layer 303 is formed in the mask layer 305a .

[0056] refer to Figure 13 ,right Figure 12 The mask layer 305a on both sides of the opening 311 is etched, so that the edge of the opening 311 is arc-shaped. That is, the edge of the etched mask layer 305b is arc-shaped.

[0057] In this embodiment, the method of etching the mask layer 305 a on both sides of the opening 311 is dry etching. If the etching gas can be used as CF 4 、CHF 3 , Ar, He and O 2 Mixed gas, CF 4 The flow rate is 50sccm~500sccm, CHF 3 The flow rate of Ar is 50sccm~500sccm, the flow rate of Ar is 100sccm~500sccm, the flow rate of He is 50sccm~500sccm, O 2 The flow rate is 10sccm~100sccm, the power supply is 100W~1000W, the bias source power is 100W~1000W, and the etching time is 10s~300s. But ...

no. 3 example

[0064] refer to Figure 16 A semiconductor substrate 401 is provided, and a pad oxide layer 403 and a mask layer are sequentially formed on the semiconductor substrate 401 from bottom to top.

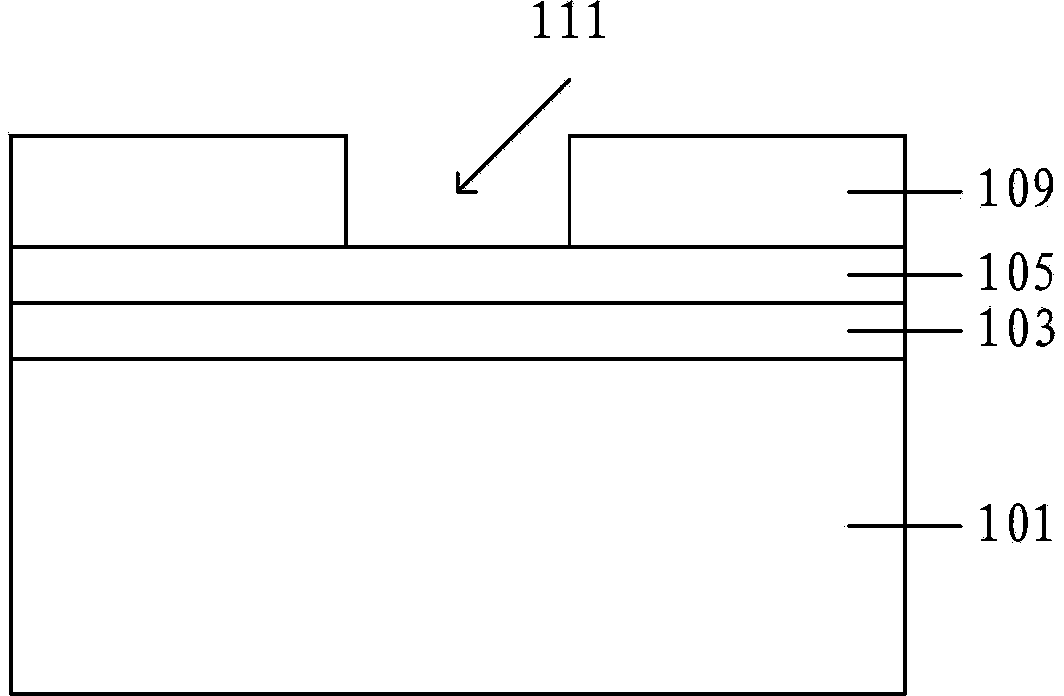

[0065] In this embodiment, the mask layer has a double-layer structure, and the mask layer includes a first mask layer 405a on the pad oxide layer 403 and a second mask layer on the first mask layer 405a 409a.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More