Technology for producing 12-inch monocrystalline silicon epitaxial wafers through pressure reduction

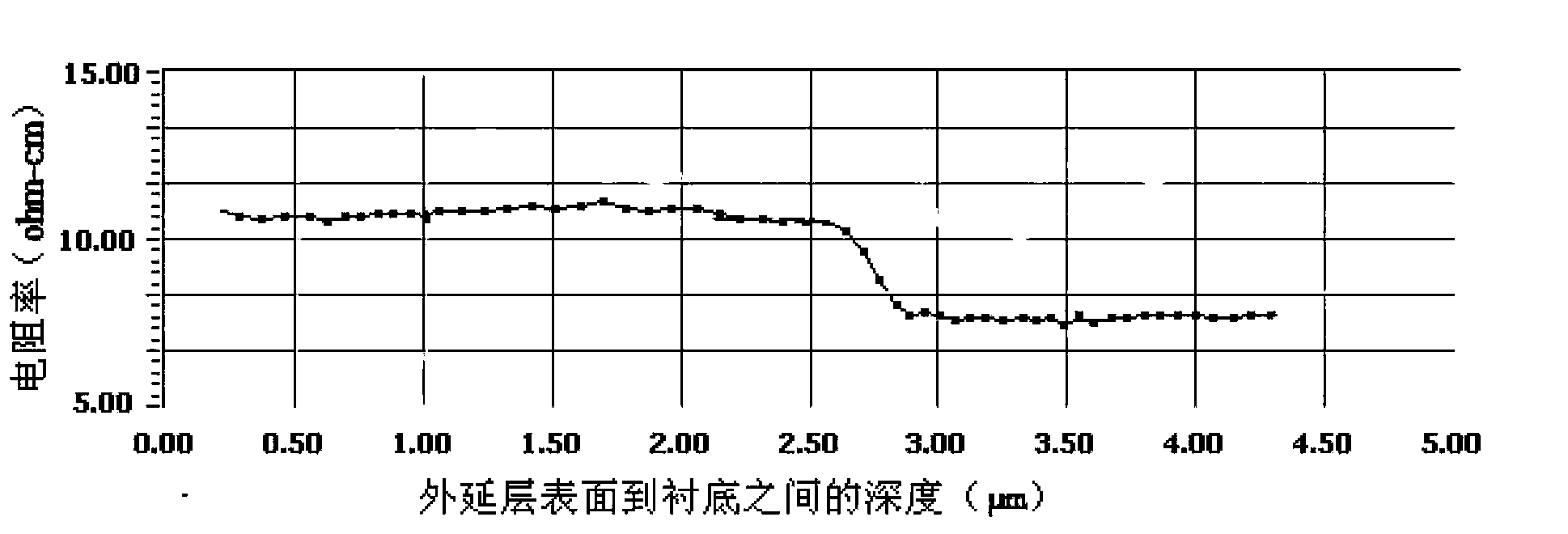

An epitaxial wafer, single crystal silicon technology, applied in the direction of single crystal growth, single crystal growth, crystal growth, etc., can solve the problems affecting the application of silicon epitaxial wafer, etc., to reduce self-diffusion effect, uniform resistivity, improve resistivity The effect of distribution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0027] When preparing to produce epitaxial wafers, ensure that the gas required for epitaxy, water cooling and other peripheral services are normal, heat the reaction chamber to 900°C, heat up for 5 to 10 minutes, heat up to 1190°C, and feed high-purity HCl gas to clean the chamber The deposition layer inside the body and on the base, and then pass through the high-purity H with a large flow rate of 50SLM 2 Purge the residual HCl gas and reaction products inside the cavity to ensure that there are as few impurities as possible in the cavity, including dopants, so as not to affect the resistivity of the epitaxial layer.

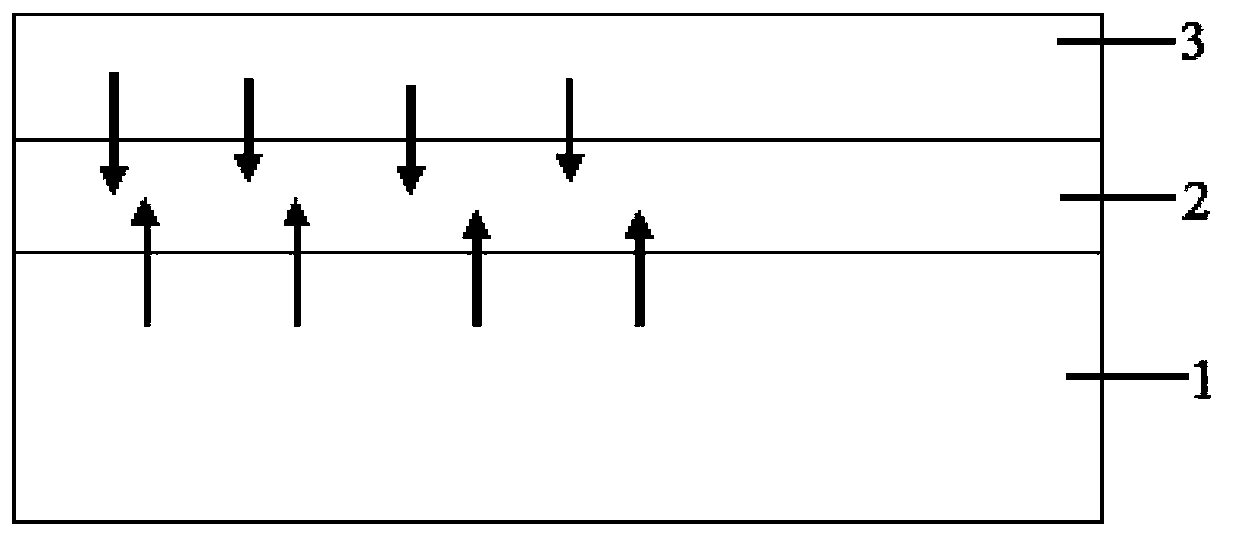

[0028] After the reaction chamber is corroded by high-purity HCl gas, its temperature is lowered to 850°C, and the 12-inch monocrystalline silicon wafer is loaded onto the reaction base by a robot, and then the pressure in the reaction chamber is reduced to 80Torr by a vacuum pump, so that The 12-inch monocrystalline silicon wafer is in a decompressed environm...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More