Method for reducing ohmic contact resistance of HEMT device

A technology of ohmic contact and resistance, applied in semiconductor devices, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as surface topography and edge uniformity, GaN material damage, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

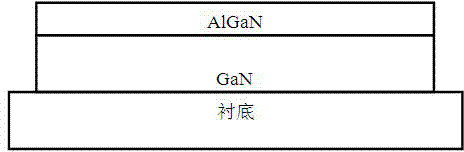

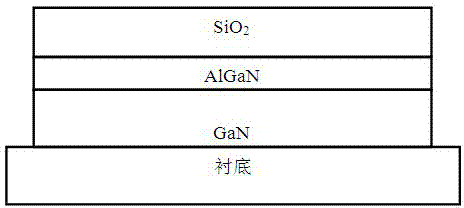

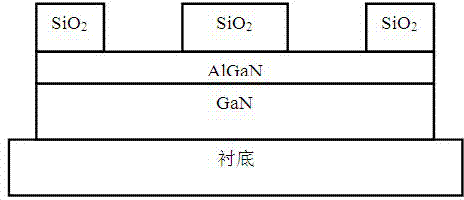

[0038] In this embodiment, the AlGaN / GaN HEMT device material is taken as an example, and the implementation mode of the present invention is described in detail in conjunction with the accompanying drawings:

[0039] figure 1 It is a schematic diagram of the general structure of AlGaN / GaN HEMT device materials; 150nm silicon dioxide (SiO2) is grown on the surface of AlGaN / GaN materials 2 ),Such as figure 2 Shown; using reactive ion etching equipment (RIE) to etch SiO in the source and drain ohmic regions of HEMT devices 2 layer to the upper surface of the AlGaN barrier layer, such as image 3 As shown; use inductively coupled plasma etching equipment (ICP) to etch the GaN material in the ohmic region of the source and drain of the HEMT device, and etch to below the AlGaN / GaN heterojunction interface (the etching depth is about 40nm), as Figure 4 Shown; above steps can be realized by prior art.

[0040] The inventive point of the present invention is that after secondar...

Embodiment 2

[0044] In this embodiment, taking the InAlN / GaN HEMT device material as an example, the implementation of the present invention is described in detail:

[0045] Growth of 200nm silicon dioxide (SiO2) on the surface of InAlN / GaN material 2 ) layer; use reactive ion etching equipment (RIE) to etch SiO in the source and drain ohmic regions 2 Layer to the upper surface of the InAlN barrier layer; use inductively coupled plasma etching equipment (ICP) to etch the GaN material in the ohmic region of the source and drain of the HEMT device, etch below the InAlN / GaN heterojunction interface (the etching depth is about 30nm ); the above steps can be realized by prior art.

[0046] Then, use MOCVD equipment to epitaxially secondarily 60nm n-type heavily doped GaN material in the source-drain ohmic region after the treatment of the above device; and then anneal in a high-temperature annealing furnace at 300°C for 3 minutes in a high-purity nitrogen atmosphere to obtain the obtained req...

Embodiment 3

[0048] In this embodiment, an InAlN / GaN HEMT device material is taken as an example to describe the implementation of the present invention in detail. In this embodiment, the focus is on the adjustment of process parameters.

[0049] Growth of 200nm silicon dioxide (SiO2) on the surface of InAlN / GaN material 2 ) layer; use reactive ion etching equipment (RIE) to etch SiO in the source and drain ohmic regions 2 Layer to the upper surface of the InAlN barrier layer; use inductively coupled plasma etching equipment (ICP) to etch the GaN material in the ohmic region of the source and drain of the HEMT device, etch below the InAlN / GaN heterojunction interface (the etching depth is about 50nm ); the above steps can be realized by prior art. Then, use MOCVD equipment to epitaxially secondarily 60nm n-type heavily doped GaNN material in the source-drain ohmic region after the above-mentioned device processing; and then anneal in a high-temperature annealing furnace at 800°C for 0.5 m...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More