Router structure capable of sharing and self-configuring cache

A router and self-configuration technology, applied in the direction of instruments, electrical digital data processing, digital transmission systems, etc., can solve problems such as imbalance and high throughput characteristics of NoC systems, reduce delay, increase adaptability, and improve throughput. rate effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach

[0022] According to above explanation content, the specific implementation mode of the present invention is as follows:

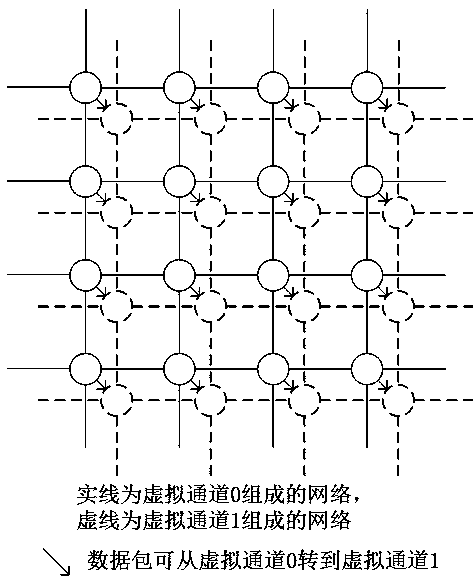

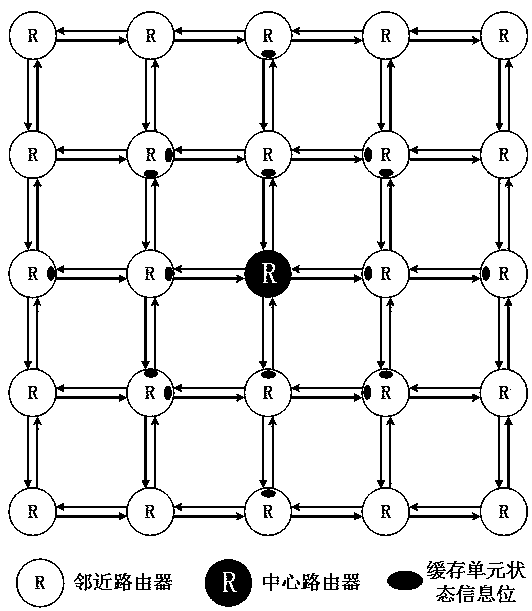

[0023] (1) The four ports in the southeast and northwest of each router contain a cache unit respectively. The cache unit completes the handshake communication between routers and is also used to cache the data of each input port. The cache adopts a first-in-first-out queue, which can realize asynchronous communication. The specific structure is shown in Figure 2. Each buffer unit contains three first-in-first-out queues, where FIFOa has a depth of 8, and FIFOb and FIFOc both have a depth of 4. All FIFOa of all routers in the entire network-on-chip form a virtual channel 0, and all FIFOb and FIFOc of all routers form a virtual channel 1, but there is only one physical channel between adjacent routers. When the FIFOa of a certain port is in a busy state, it can temporarily buffer the next input data in the port or (and) the FIFOc of two adjacent ports, prov...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More