Low-temperature poly-silicon manufacturing method, method for manufacturing TFT substrate by utilization of low-temperature poly-silicon manufacturing method, and TFT substrate structure

A technology of low-temperature polysilicon and a manufacturing method, which is applied to the manufacturing method and structure of TFT substrate, and the manufacturing field of low-temperature polysilicon, can solve the problems of very strict requirements on mask precision and difficulty in mass production, so as to improve display effect and reduce crystallinity. The number of bounds, the effect of the simple method

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0054] In order to further illustrate the technical means adopted by the present invention and its effects, the following describes in detail in conjunction with preferred embodiments of the present invention and accompanying drawings.

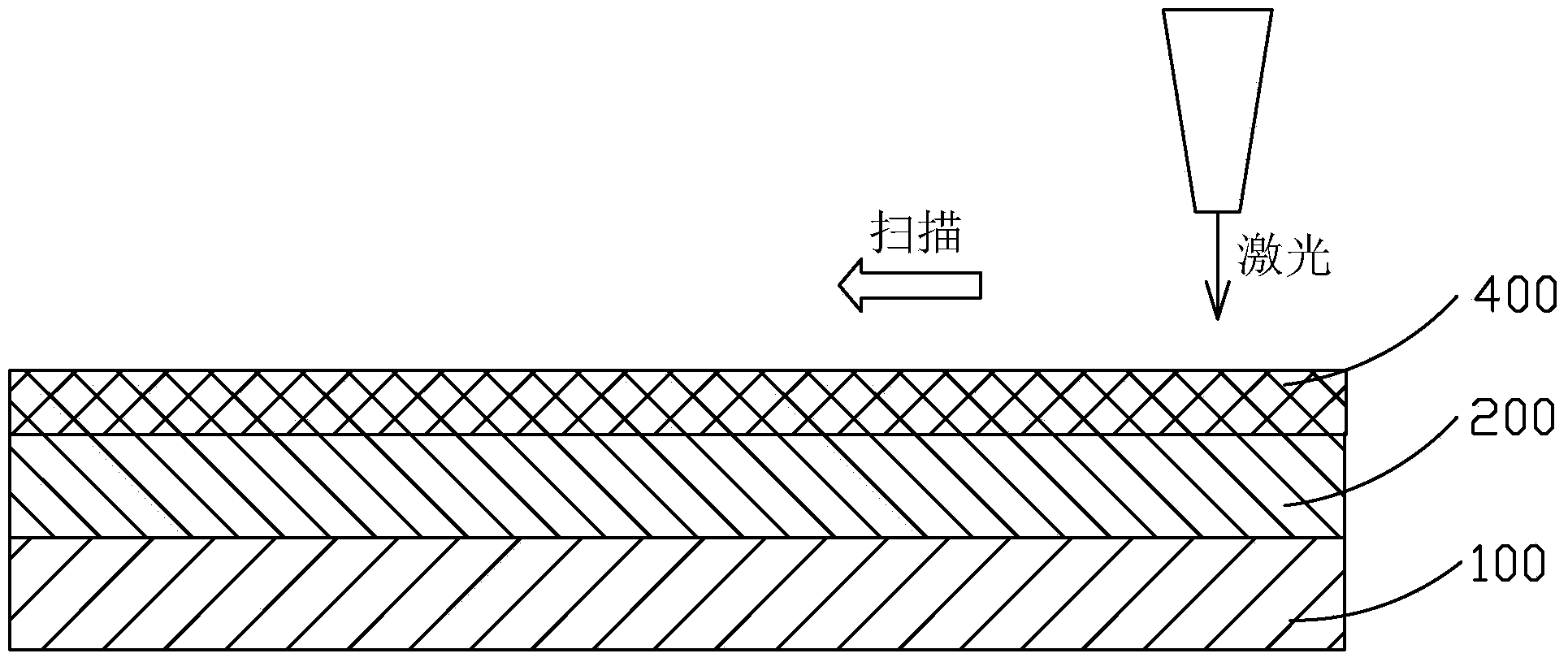

[0055] see Figure 6 and Figure 8 to Figure 13 , the invention provides a method for manufacturing low-temperature polysilicon, comprising the steps of:

[0056] Step 1, providing a substrate 1 .

[0057] The substrate 1 is a transparent substrate, preferably, the substrate 1 is a glass substrate.

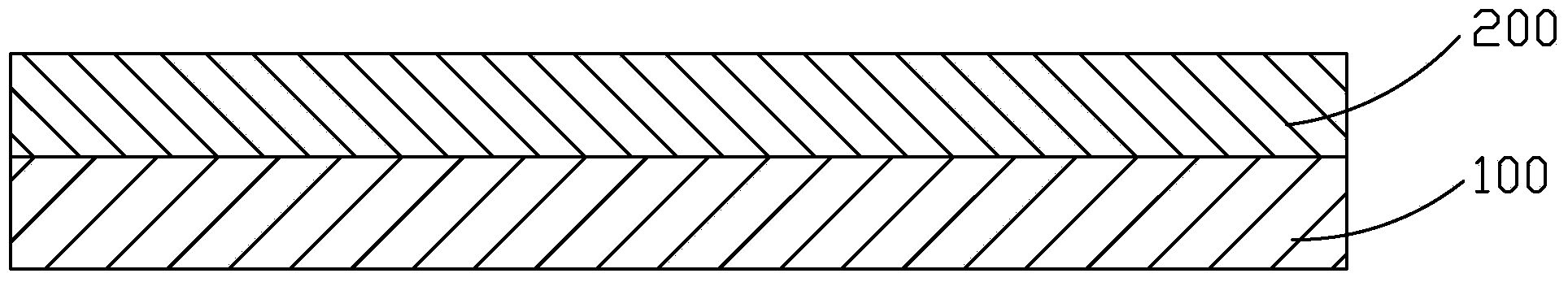

[0058] Step 2, depositing and forming a buffer layer 2 on the substrate 1 .

[0059] Such as Figure 8 As shown, the thickness of the buffer layer 2 deposited and formed in step 2 is uniform. The buffer layer 2 is made of SiNx, SiOx, or a combination of SiNx and SiOx.

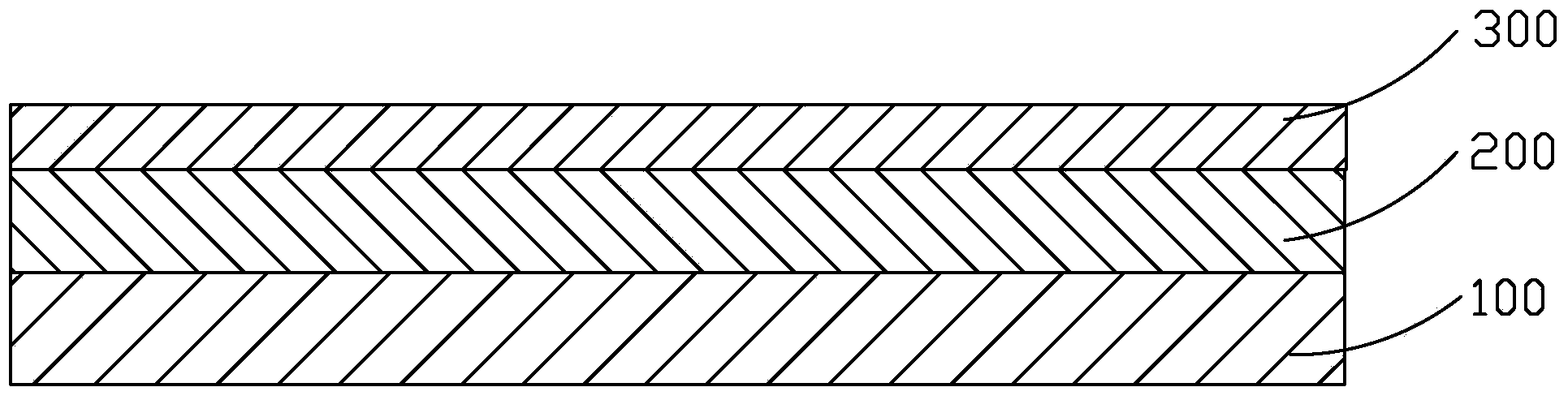

[0060] Step 3, patterning the buffer layer 2 to form protrusions 21 and depressions 23 with different thicknesses.

[0061] Such as Figure 9 , Figure 10 As shown, there ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More