P-type epitaxial layer of LED, manufacturing method thereof and LED epitaxial wafer comprising thereof

A manufacturing method and epitaxial layer technology, applied in the direction of electrical components, circuits, semiconductor devices, etc., can solve the problems of inability to effectively block electron migration, InGaN layer precipitation, and reduce luminous efficiency, so as to reduce damage, improve luminous efficiency, The effect of improving the mobility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

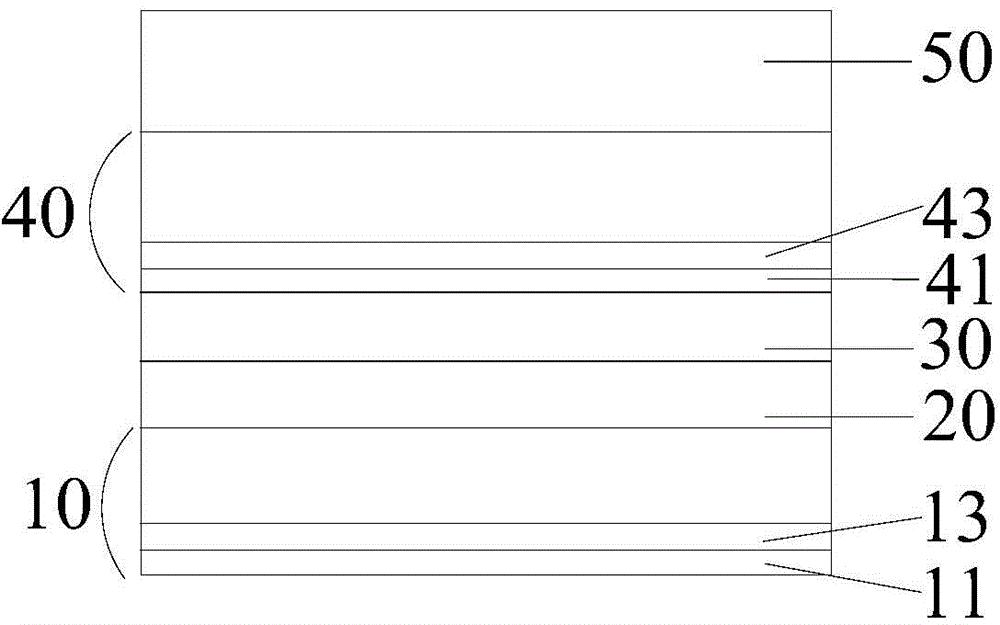

[0055] As an example, an optional implementation of forming a GaN buffer layer, u-type GaN, n-type epitaxial layer and quantum well layer is given below, including the following steps:

[0056] Place the sapphire substrate in the MOCVD reaction chamber, and use H 2 or NH 3 Wait for the gas to treat the sapphire substrate at high temperature for 5 to 10 minutes;

[0057] Lower the temperature in the reaction chamber to 500-600°C (the optimum temperature is 550°C), and feed TMGa and NH 3 , the pressure is controlled at 300torr~650torr, and a GaN buffer layer with a thickness of 15~40nm is grown on the sapphire substrate;

[0058] Raise the temperature to 950-1100°C, high-temperature annealing for 200-500s; adjust the temperature to 1000-1100°C, and feed TMGa and NH 3 , the pressure is controlled at 300torr~700torr, the first u-type GaN with a thickness of 0.8~1.2um is grown on the GaN buffer layer, and then the temperature is raised to 1050~1100℃, the pressure is controlled a...

Embodiment 1

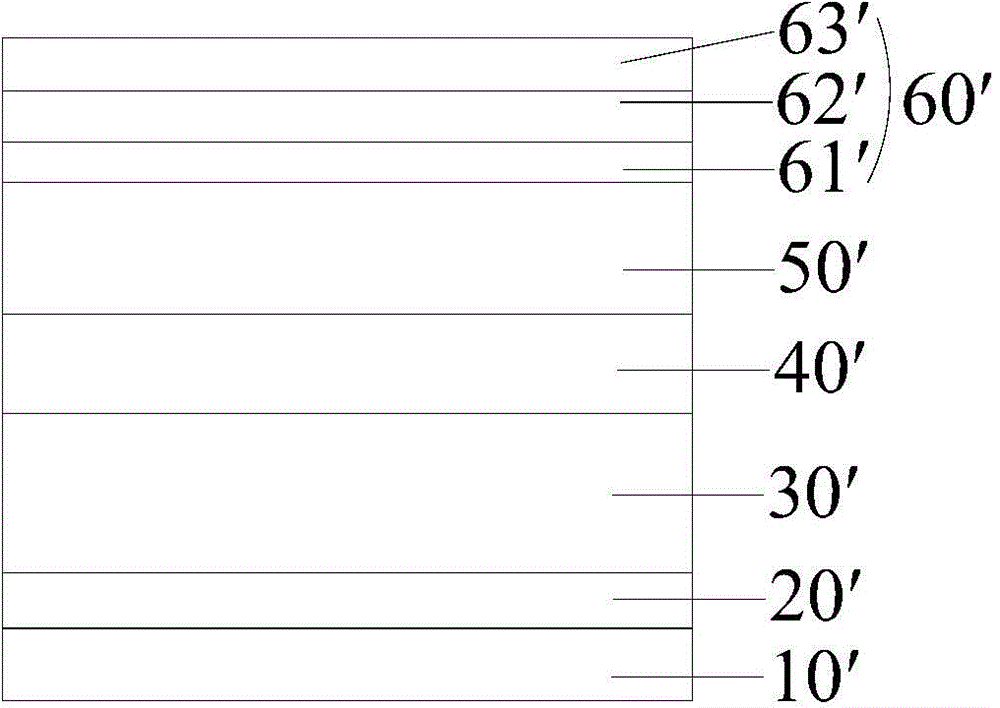

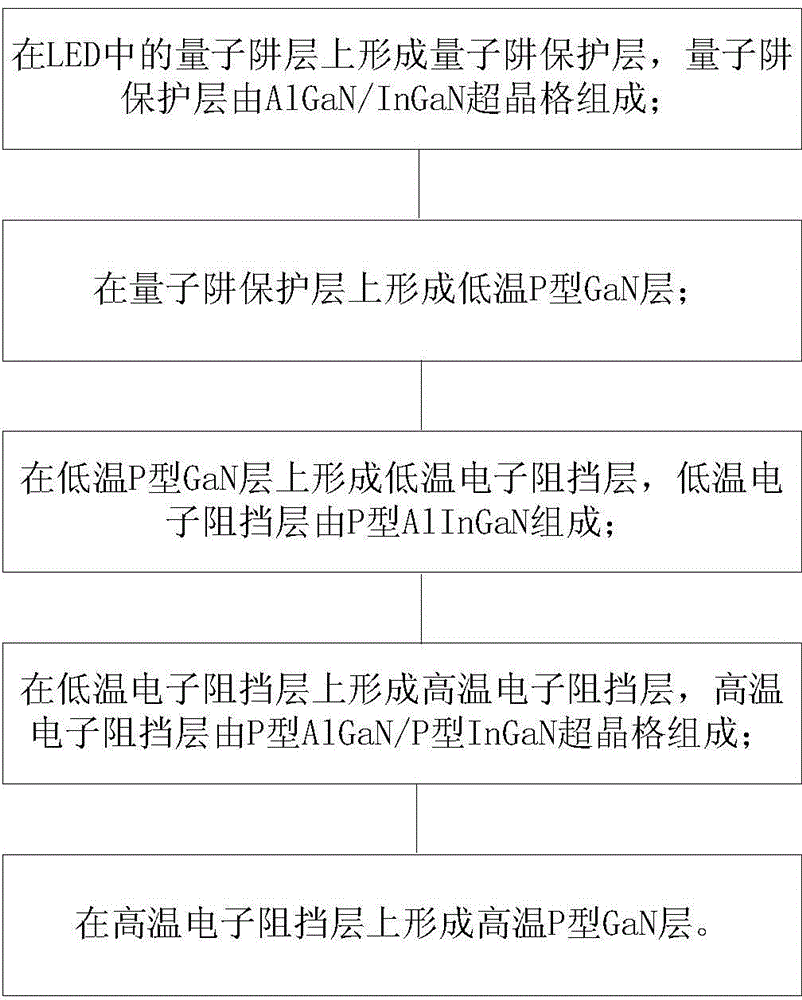

[0067] This embodiment provides a method for manufacturing an LED epitaxial wafer, including sequentially forming a GaN buffer layer, u-type GaN, n-type epitaxial layer, stress release layer, quantum well layer, and p-type epitaxial layer on a sapphire substrate along the direction away from the sapphire substrate. The step of epitaxial layer, wherein the step of forming P-type epitaxial layer comprises:

[0068] A quantum well protective layer (composed of AlGaN / InGaN superlattice) is grown on the quantum well layer (MQW), where the growth conditions are controlled at a pressure of 100torr-300torr, and the temperature is adjusted to 830°C to grow the AlGaN / InGaN superlattice layer, AlGaN The thickness of the single layer is controlled at 2nm, the thickness of the InGaN single layer is controlled at 2nm, the cycle is 5, and the total thickness is controlled at 20nm;

[0069] The temperature is adjusted to 780°C, the pressure is controlled at 100torr, and the concentration of M...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More