On-chip oscillator circuit capable of eliminating control logic delay

A technology for controlling logic and oscillators, applied in electrical pulse generator circuits, electrical components, generating electrical pulses, etc., can solve the problems of reducing temperature coefficient, affecting reliability, inconsistent clock frequency voltage coefficient and temperature coefficient, etc. Reduced voltage coefficient and temperature coefficient, simple circuit structure, and low cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

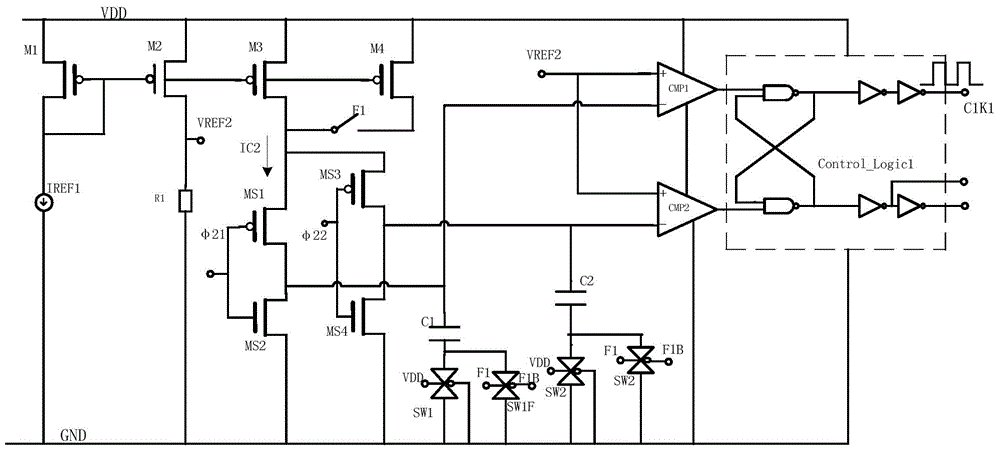

[0023] see figure 2 , shows the oscillator circuit that eliminates the control logic delay implemented by the present invention, wherein the reference current IREF1 is mapped through the current mirror M1 to M2, flows through R1 to generate the first reference voltage VREF2, and the second reference voltage is the reference ground, The current mirror M3 generates the first charge and discharge current IC2, one of the first charge and discharge switch groups is composed of PMOS switch MS1+NMOS switch MS2, the upper end of the first charge and discharge switch group is connected to the drain of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More