A double-ring through-silicon via structure and its manufacturing method

A manufacturing method, ring silicon technology, applied in the direction of semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as lack of shielding signal noise, signal channel coupling, increased crosstalk, and large metal thermal stress, etc., to achieve High frequency signal integrity, improved thermomechanical properties, and reduced thermal stress

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment 1

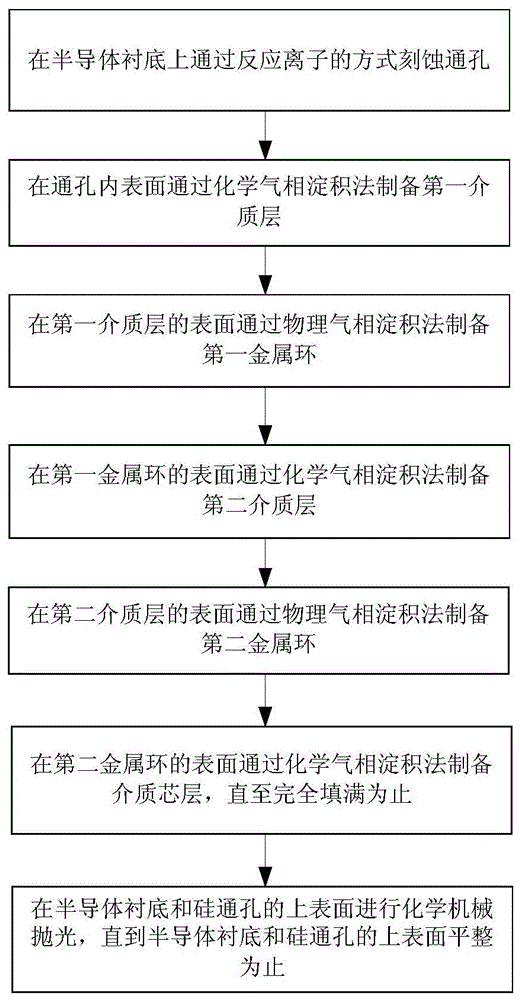

[0036] Such as figure 1 with Figure 3-9 As shown, a method for manufacturing double-ring TSVs includes the following steps:

[0037] (1) On the semiconductor substrate 1, the through hole is etched by means of reactive ions. The semiconductor substrate 1 is a silicon substrate, and its height is 50 μm, and its length and width are 5 mm; the aperture of the through hole is 5.1 μm; step (1 ) The process conditions for reactive ion etching through holes are: use fluoride or chloride gas, decompose fluorine atoms or chlorine atoms in glow discharge, and react with surface silicon atoms to form gaseous products to achieve the purpose of etching; The gas pressure is 15-30 pascals, the reaction gas flow rate is 10-40 ml / min, and the radio frequency power range is 200-350 watts. At the same time, the heat exchanger and the helium cooling technology on the back of the silicon wafer are used for temperature control to ensure that the temperature of the entire silicon wafer is uniform...

specific Embodiment 2

[0054] The preparation process is roughly the same as in Example 1, except that the aperture of the through hole in step (1) is 15 μm;

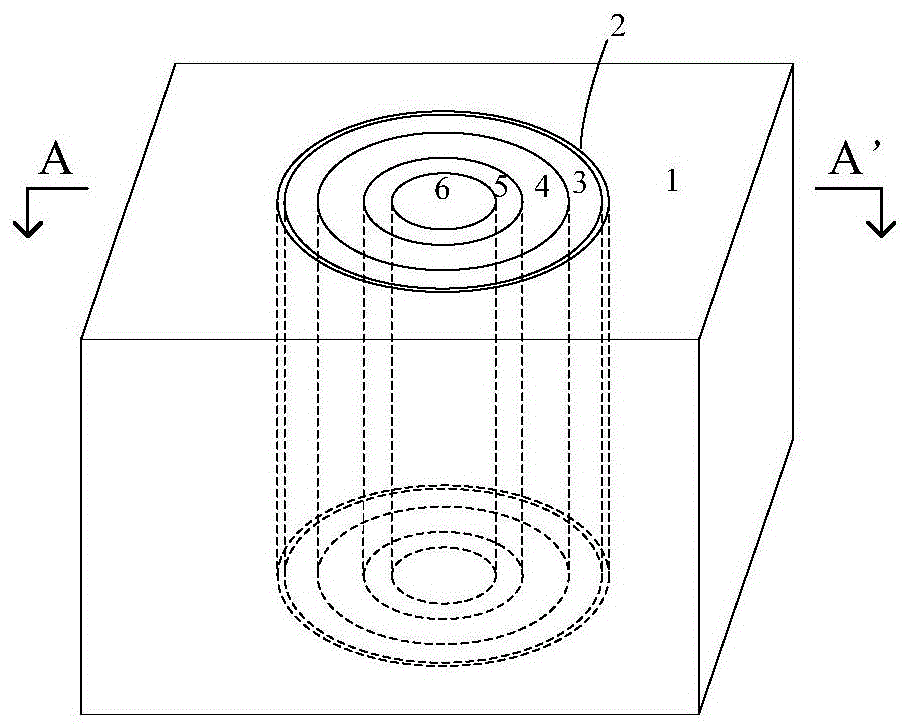

[0055] A double-ring through-silicon via structure, which includes a semiconductor substrate, a first dielectric layer 2, a first metal ring 3, a second dielectric layer 4, a second metal ring 5, and a dielectric core layer 6 from outside to inside.

[0056] The first dielectric layer 2 is a silicon nitride layer, and the thickness of the first dielectric layer 2 is 1 μm;

[0057] The thickness of the first metal ring 3 is 3 μm;

[0058] The second dielectric layer 4 is a silicon nitride layer, and the thickness of the second dielectric layer 4 is 3 μm;

[0059] The thickness of the second metal ring 5 is 3 μm;

[0060] The dielectric core layer 6 is a silicon nitride core layer, and the radius of the dielectric core layer 6 is 5 μm.

[0061] In this embodiment, the semiconductor substrate is a silicon substrate.

[0062] In this embodime...

specific Embodiment 3

[0066] The preparation process is roughly the same as that of Example 1, except that the diameter of the through hole in step (1) is 9.5 μm;

[0067] A double-ring through-silicon via structure, which includes a semiconductor substrate, a first dielectric layer 2, a first metal ring 3, a second dielectric layer 4, a second metal ring 5, and a dielectric core layer 6 from outside to inside.

[0068] The first dielectric layer 2 is a silicon oxynitride layer, and the thickness of the first dielectric layer 2 is 0.5 μm;

[0069] The thickness of the first metal ring 3 is 2 μm;

[0070] The second dielectric layer 4 is a silicon oxynitride layer, and the thickness of the second dielectric layer 4 is 2 μm;

[0071] The thickness of the second metal ring 5 is 2 μm;

[0072] The dielectric core layer 6 is a silicon oxynitride core layer, and the radius of the dielectric core layer 6 is 3 μm.

[0073] In this embodiment, the semiconductor substrate is a silicon substrate.

[0074]...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| radius | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More