Method for forming semiconductor structure

A technology of semiconductor and gate structure, which is applied in the field of formation of semiconductor structures, can solve the problems of increased difficulty of FinFET process and performance degradation of FinFET, and achieves the effect of stable and accurate performance and precise feature size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] As mentioned in the background art, in the prior art, the process of forming a fin field effect transistor is relatively difficult, and the formed fin field effect transistor has poor performance.

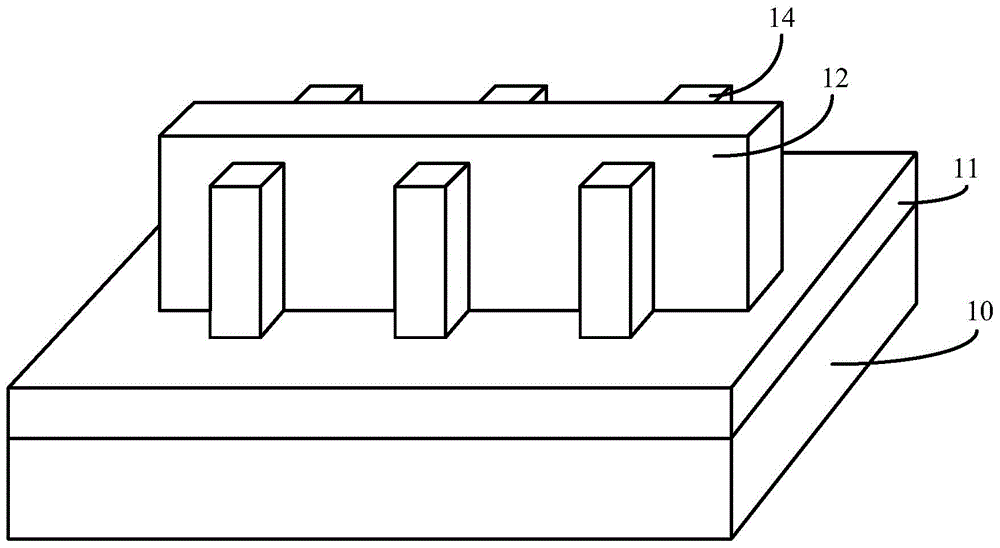

[0029] As the process node shrinks, the size of the fins and the distance between adjacent fins also shrink accordingly, resulting in poor quality of the gate dielectric layer and gate electrode layer formed on the sidewalls and top surfaces of the fins. Please continue to refer figure 1 The method for forming a gate structure on the surface of the fin in the prior art includes: using a deposition process to form a gate dielectric film on the surface of the dielectric layer 11, and the sidewall and top surface of the fin 14; forming a gate electrode on the surface of the gate dielectric film Thin film: using an anisotropic dry etching process to etch part of the gate electrode film and gate dielectric film until the top and sidewall surfaces of the fin 14 and the surface of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More