Self-gating resistance-variable memory unit and preparation method thereof

A technology of resistive memory and self-selection, which is applied in the field of microelectronics, can solve the problems of integration scale and read and write operation limitations, lack of a single device patterning process, difficulty in gate tube integration, etc., to achieve simple structure and suppress read crosstalk phenomenon , Realize the effect of three-dimensional storage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

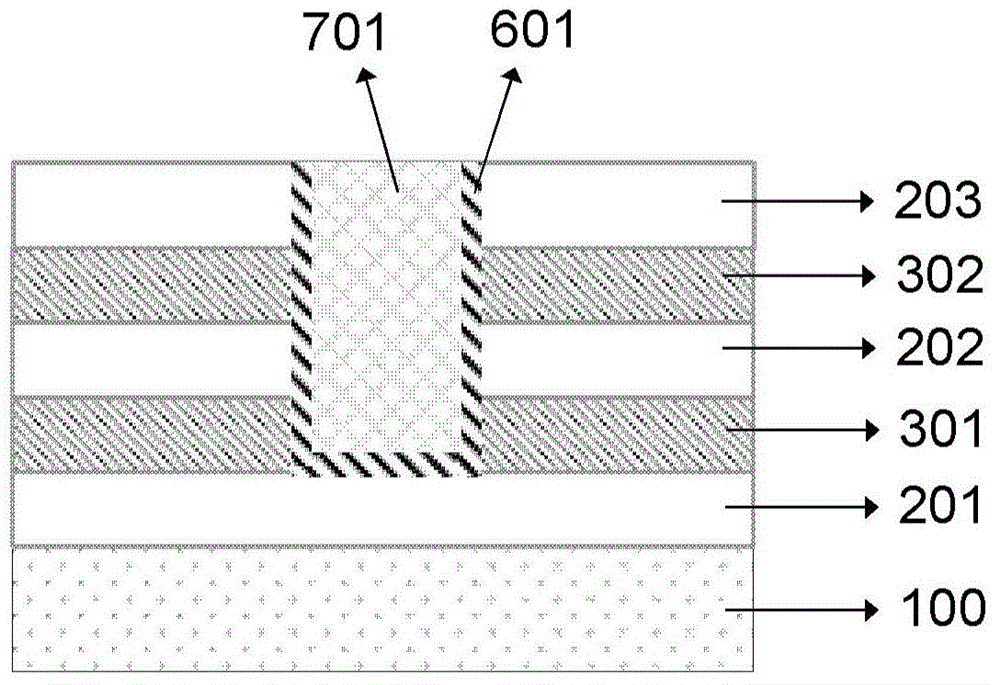

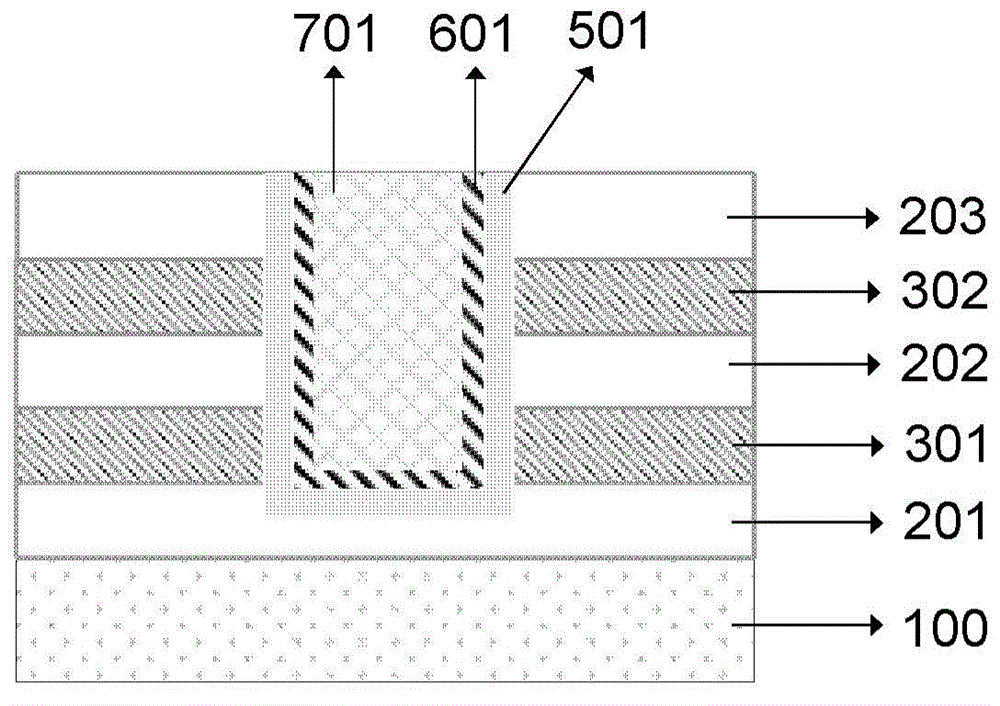

[0042] The invention is described more fully hereinafter in reference to the examples illustrated in the illustrations, providing preferred embodiments but should not be considered limited to the embodiments set forth herein. In the drawings, the thicknesses of layers and regions are exaggerated for clarity, but as schematic diagrams, they should not be considered as strictly reflecting the proportional relationship of geometric dimensions. The drawings referenced herein are schematic illustrations of idealized embodiments of the invention, and the illustrated embodiments of the invention should not be considered limited to the particular shapes of the regions shown in the drawings, but include the resulting shapes, the representations in the drawings are illustrative, but should not be construed as limiting the scope of the invention.

[0043] The self-selectable resistive memory unit provided by the present invention includes: a stacked structure comprising a multi-layer con...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More