Thin film transistor manufacturing method

A technology of thin film transistors and manufacturing methods, which is applied in the field of Lig, can solve the problems of uniformity reduction, influence on TFT electrical properties, influence on gate oxide layer thickness and step coverage, etc., to improve uniformity, reduce bump height, and display effect better effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] In order to facilitate a further understanding of the method and the achieved effects of the present invention, preferred embodiments are described in detail below in conjunction with the accompanying drawings.

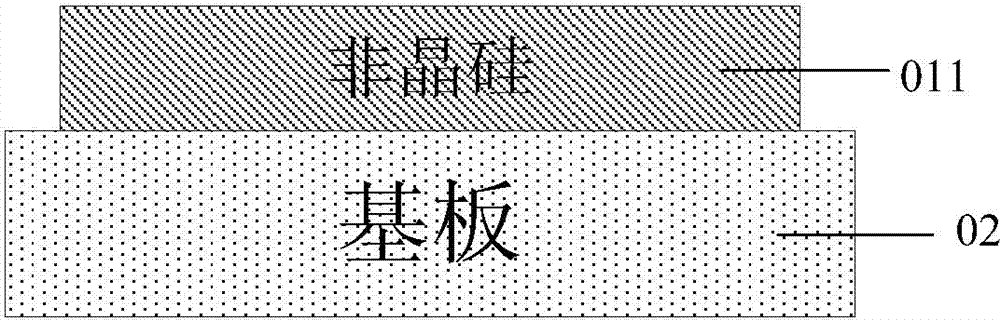

[0028] refer to Figure 8 The process flow chart of the present invention and other drawings of the present invention, first utilize CVD (Chemical Vapor Deposition, chemical vapor deposition) deposition method to deposit a layer of amorphous silicon 011 on the TFT substrate 02, such as figure 1 As shown in the schematic diagram of the deposition structure, the substrate 02 is a glass substrate, and the thickness of the amorphous silicon 011 film is 300-1000 Å.

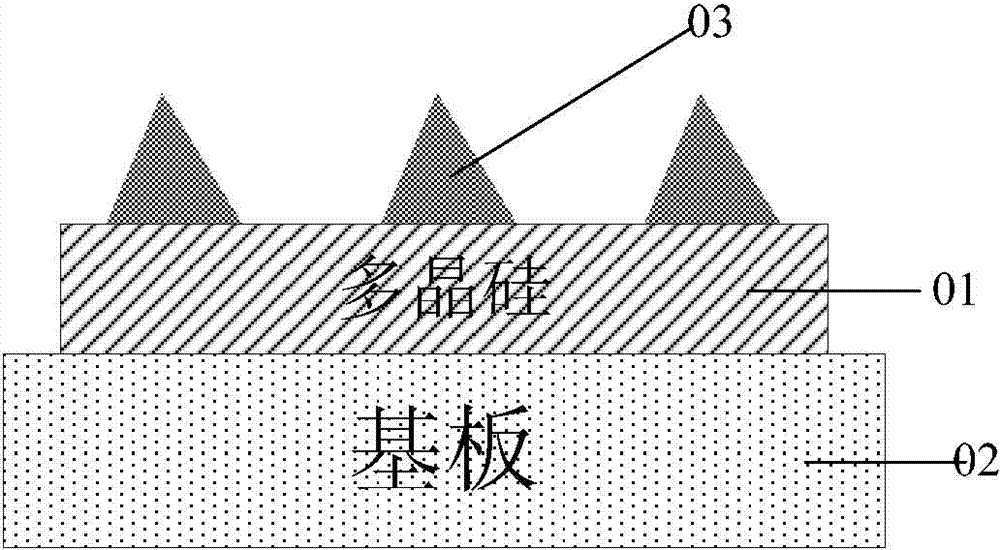

[0029] Use ELA (excimer laser annealing) technology to crystallize amorphous silicon 011 to become polysilicon 01. During the crystallization process, a large number of protrusions 03 are generated on the surface of polysilicon 01 due to ELA crystallization, such as figure 2 Shown is a schematic stru...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More