Detection structure for wafer bonding, preparation method and detection method

A detection structure, wafer bonding technology, applied in the direction of microstructure technology, microstructure devices, manufacturing microstructure devices, etc., can solve the problems of unusable devices, inability to monitor wafers, destructive detection, etc., and achieve a wide coverage area Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

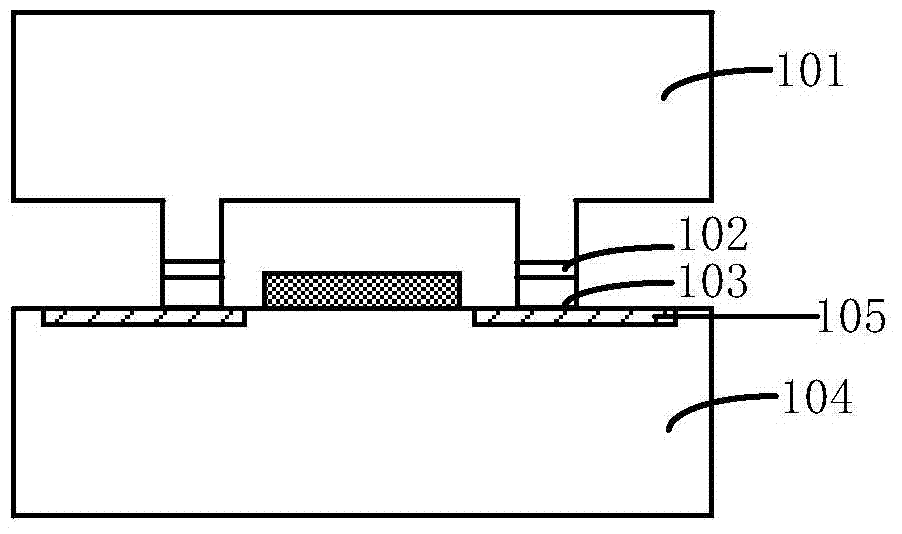

[0062] Figure 2e Is a schematic structural diagram of a test structure in a specific embodiment of the present invention, where Figure 2e The figure on the right is a partial enlarged view of the marked area in the figure on the left;

[0063] The test structure includes a junction between two wafers, where the wafer below is a wafer forming MEMS components, and the wafer includes a semiconductor substrate (not shown in the figure), and the semiconductor Various materials commonly used in the art can be selected, and various devices, such as various CMOS devices, are also formed in the semiconductor substrate, so that the CMOS process and the MEMS process will be joined to form a CMEMS process. Both the device and the forming method can be designed and prepared as required, and will not be repeated here.

[0064] The test structure further includes a MEMS substrate 204, on which MEMS components are formed, wherein the type of the MEMS component is determined according to the type...

Embodiment 2

[0081] The present invention also provides a method for detecting the quality of wafer bonding by selecting the above-mentioned test structure. In the method, the resistance test device is connected to the interconnection metal layer 205 through a WAT probe, and the voltage is applied. In the case of measuring the resistance value, in the case of the current flow as image 3 As shown, the current enters the bonding interface described in the figure through the interconnection metal layer at one end of the MEMS substrate 204, and then enters the conductive material layer 203 through the bonding interface, and after flowing through the conductive material layer 203 Enter the bonding interface at the other end, and finally to the interconnection metal layer at the other end of the MEMS substrate 204, and then connect to the resistance test device via a WAT probe. The resistance tested in this process is the interconnection metal layer 205 , The bonding interface and the conduct...

Embodiment 3

[0089] In the present invention, the test structure is realized by changing the preparation process flow of the MEMS device without affecting the device structure. Therefore, the test structure changes the destructive test in the prior art.

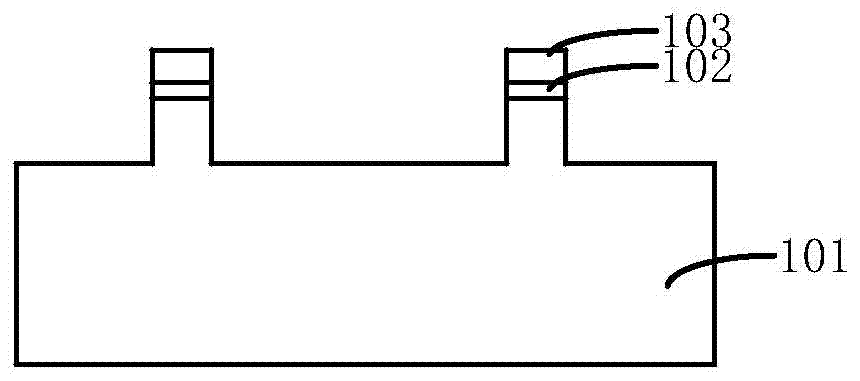

[0090] Attached below Figure 2a-2e The preparation method of the test structure in the present invention will be further explained.

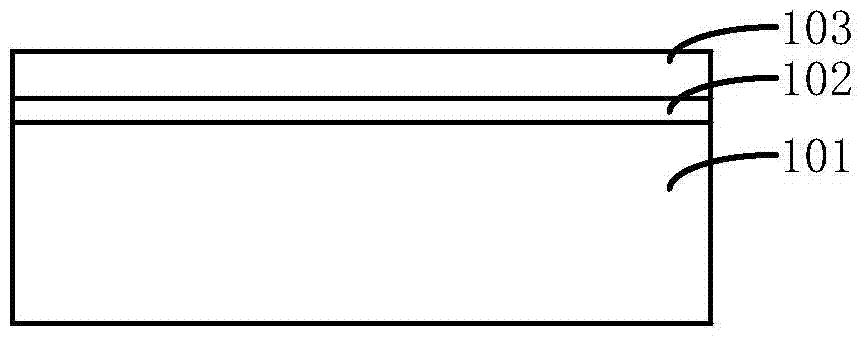

[0091] First, step 201 is performed to provide a semiconductor substrate 201, and an isolation layer 202 is formed on the semiconductor substrate 201.

[0092] Specifically, refer to Figure 2a The semiconductor substrate 201 can be a commonly used semiconductor material. In this embodiment, the semiconductor substrate 201 is silicon.

[0093] Wherein, the isolation layer 202 can be made of commonly used insulating materials, such as SiO 2 , SiN, carbon-doped silicon oxide (SiOC), or silicon carbonitride (SiCN), etc. Alternatively, a film in which a SiCN thin film is formed on a fluorocarbon (CF) can also be used....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More