Method for Increasing Control Gate Height of Split Gate Flash Memory

A memory and control gate technology, applied in the direction of electric solid-state devices, semiconductor devices, electrical components, etc., can solve the problems of easy penetration, PTC, residue, etc., and achieve the effects of improving device performance, avoiding penetration, and high recess height

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

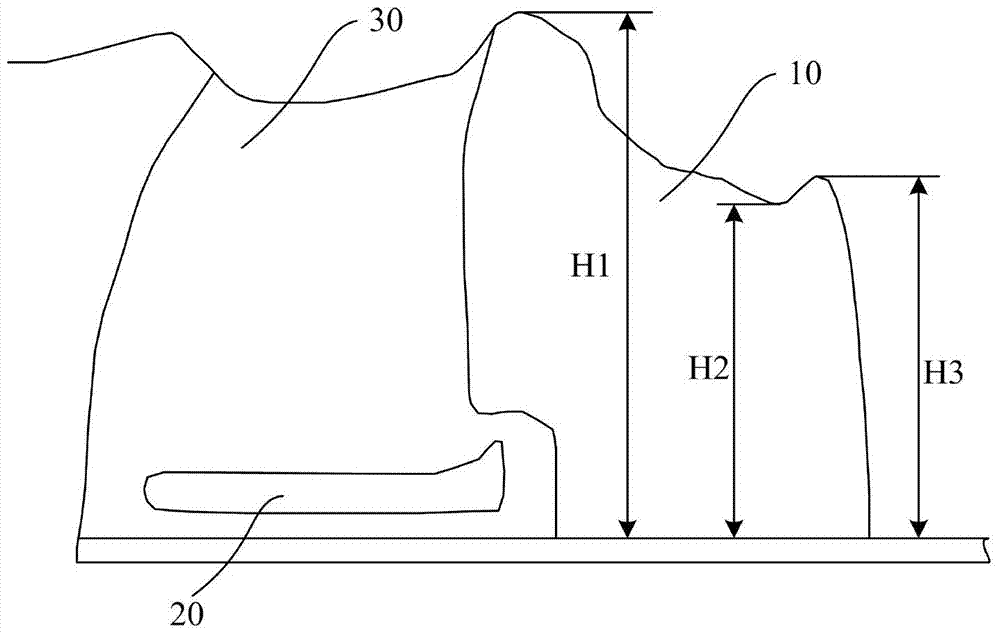

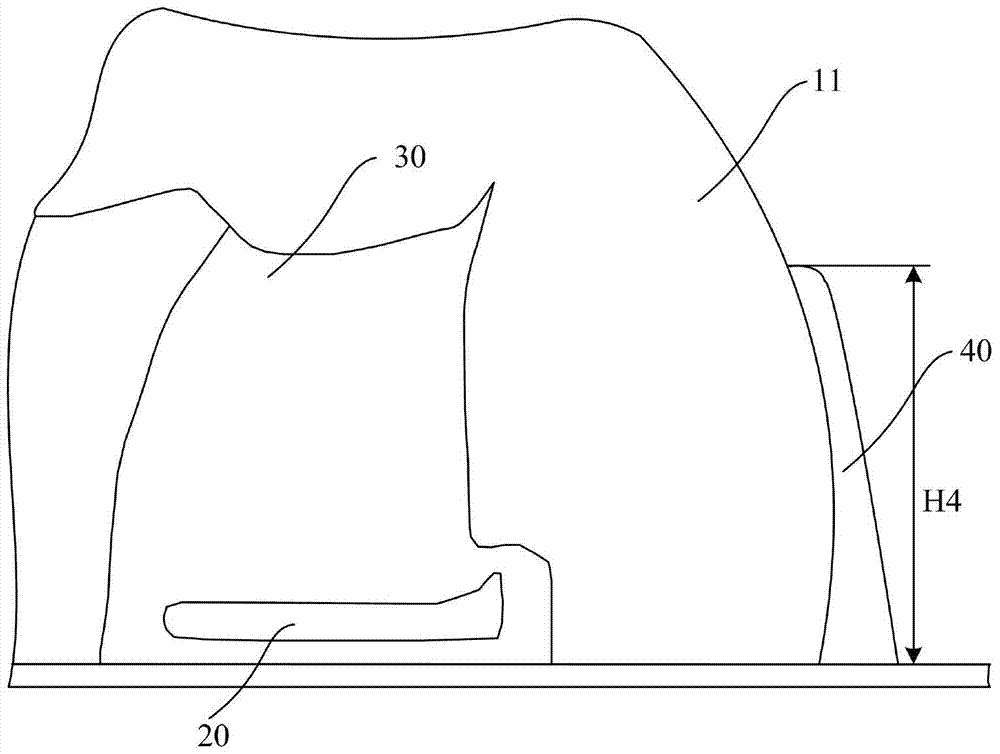

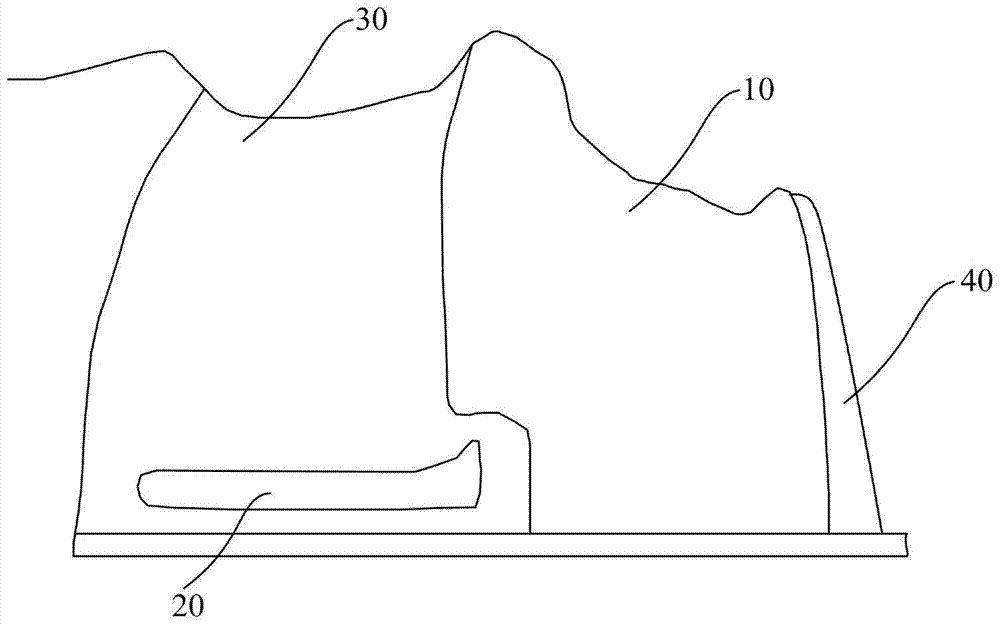

[0034] The method for increasing the height of the control gate of the sub-gate flash memory of the present invention will be described in more detail below in conjunction with the schematic diagram, wherein a preferred embodiment of the present invention is shown, it should be understood that those skilled in the art can modify the present invention described herein, and The advantageous effects of the invention are still achieved. Therefore, the following description should be understood as the broad knowledge of those skilled in the art, but not as a limitation of the present invention.

[0035] In the interest of clarity, not all features of an actual implementation are described. In the following description, well-known functions and constructions are not described in detail since they would obscure the invention with unnecessary detail. It should be appreciated that in the development of any actual embodiment, numerous implementation details must be worked out to achiev...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com