Reinforced configuration memory array and configuration method suitable for FPGA used in aerospace

A memory array and memory cell array technology, which is applied in the field of integrated circuits, can solve the problems that the configuration memory array cannot work normally, the FPGA consumes a lot of current, and affects the realization of system functions, so as to solve the problem of power-on surge current and improve the Maximum operating speed and frequency, the effect of improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

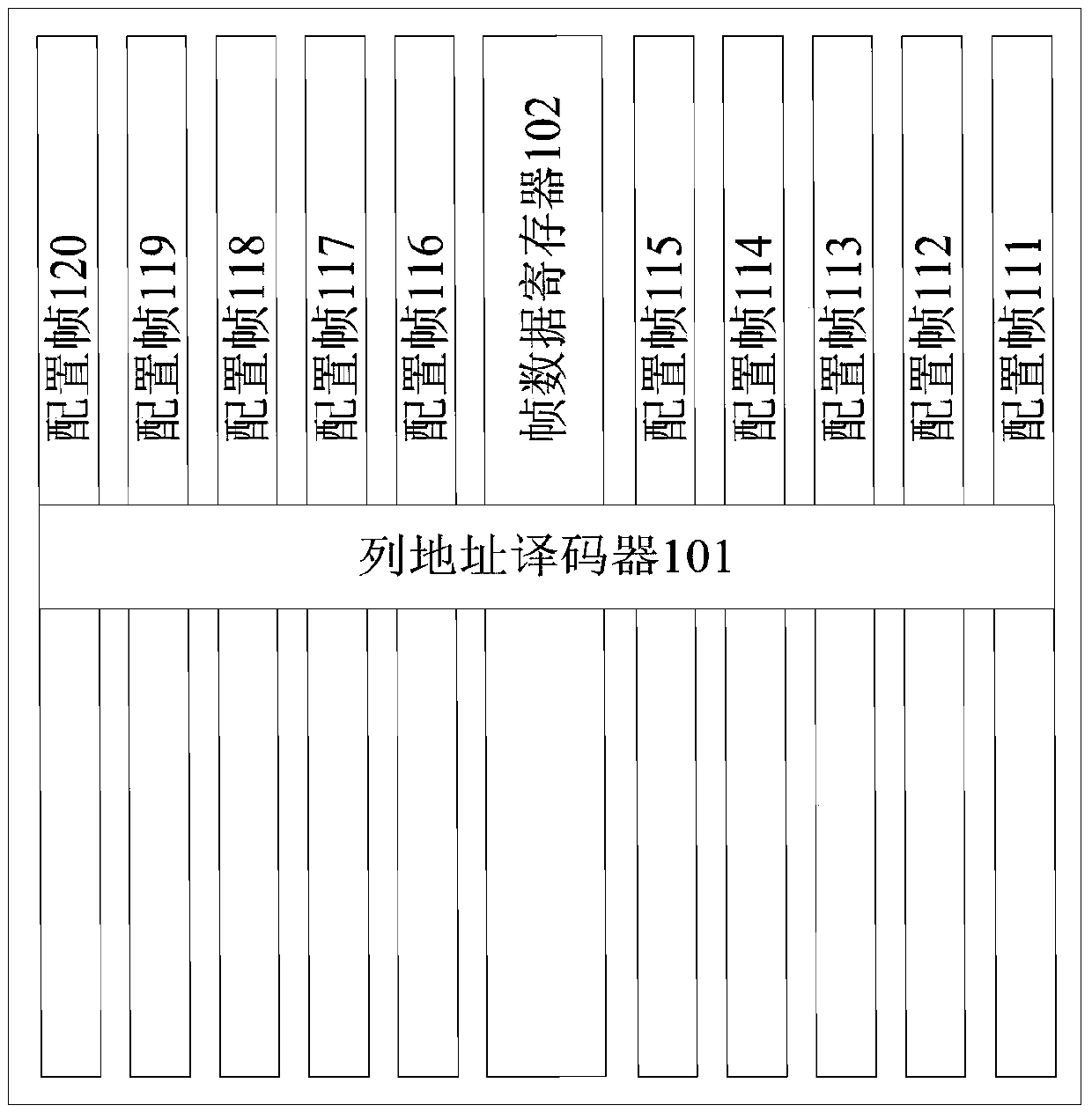

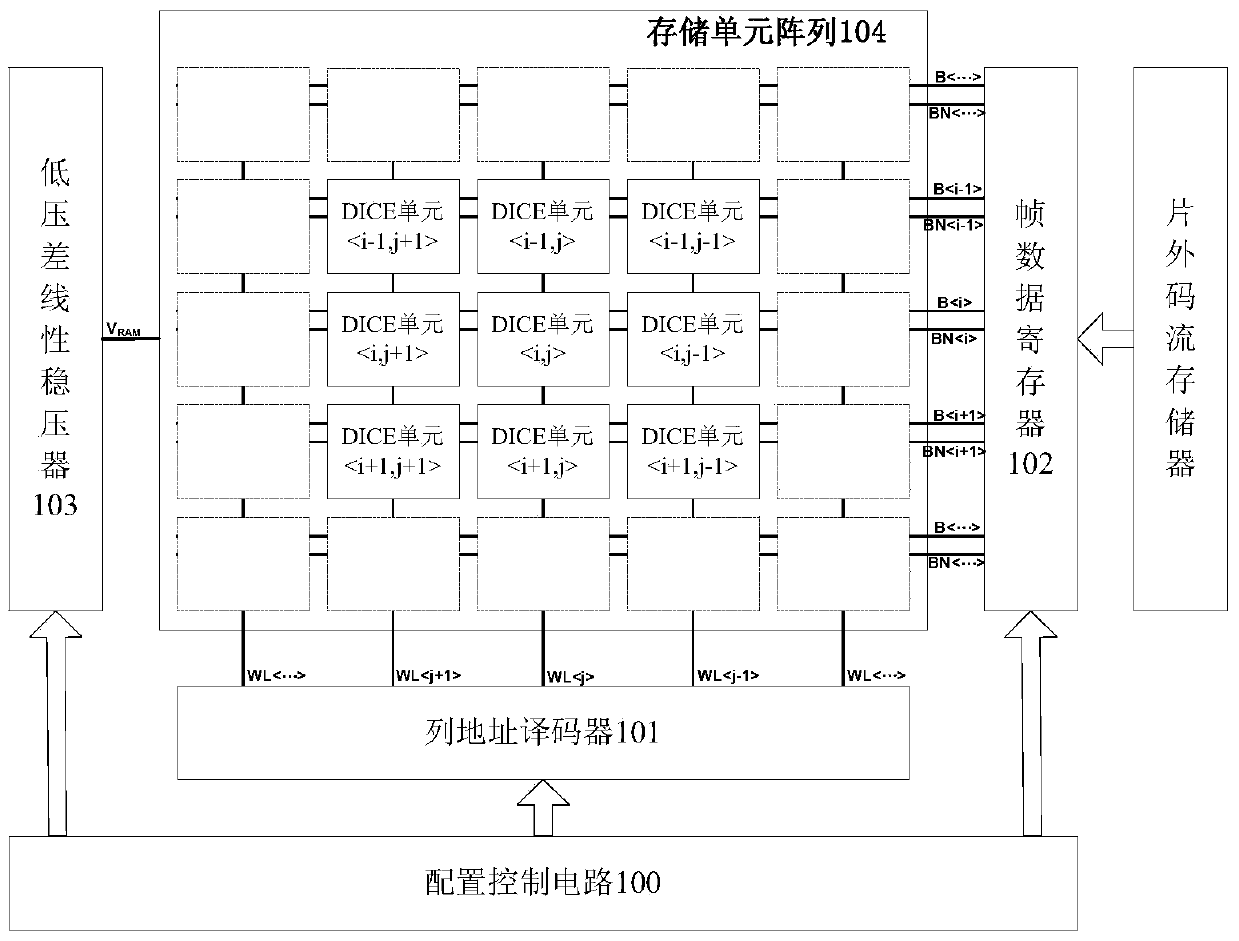

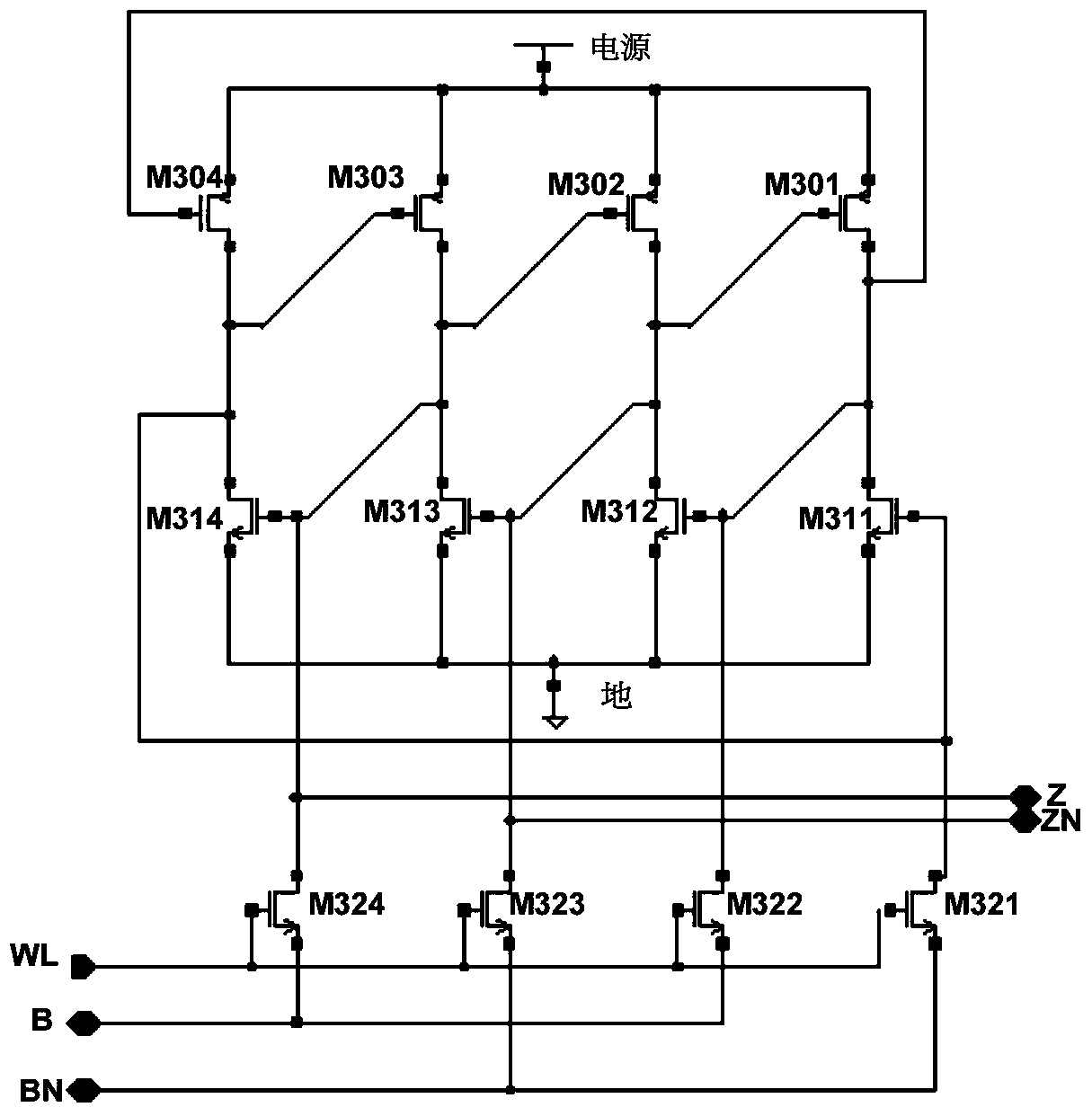

[0034] In order to eliminate, suppress or reduce the impact of single event effects on system functions, the present invention uses dual-node interlocked storage units (hereinafter referred to as DICE units) to carry out radiation-resistant hardening on configuration memory arrays. Such as figure 2 As shown, the configuration memory array of the present invention includes a configuration control circuit 100 , a column address decoder 101 , a frame data register 102 , a low dropout linear regulator 103 , and a memory cell array 104 . The off-chip code stream memory does not belong to the inherent structure of the configuration memory array of the present invention. The configuration control circuit 100 is connected to the column address decoder 101, the frame data register 102, and the low dropout linear voltage regulator 103, and the configuration control circuit 100 is used to control the entire configuration process, including sending power to the low dropout linear voltage...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More