Ferroelectric field effect transistor based on GeSn material, and preparation method for ferroelectric field effect transistor

An electric field effect and transistor technology, applied in the field of electronics, can solve the problems of reduced operating voltage, low electron mobility, and high power consumption of transistors, and achieve the effects of reducing device delay, high electron mobility, and low subthreshold swing.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

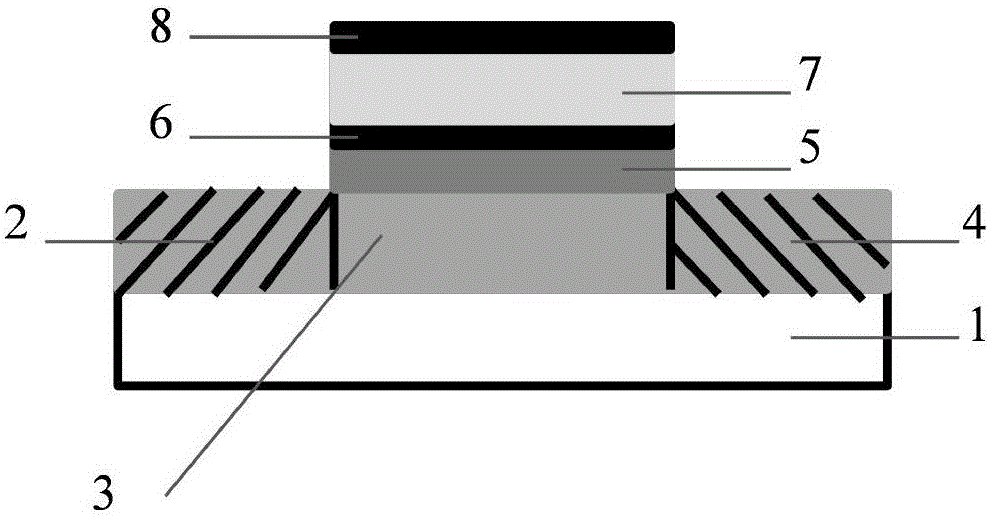

[0055] Embodiment 1: making Ge 0.935 sn 0.065 P-type ferroelectric field effect crystal.

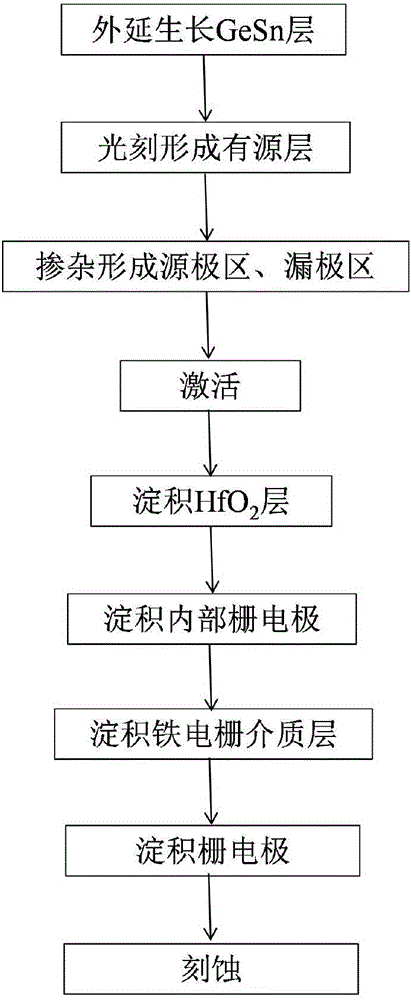

[0056] Step 1. Epitaxially grow a GeSn layer.

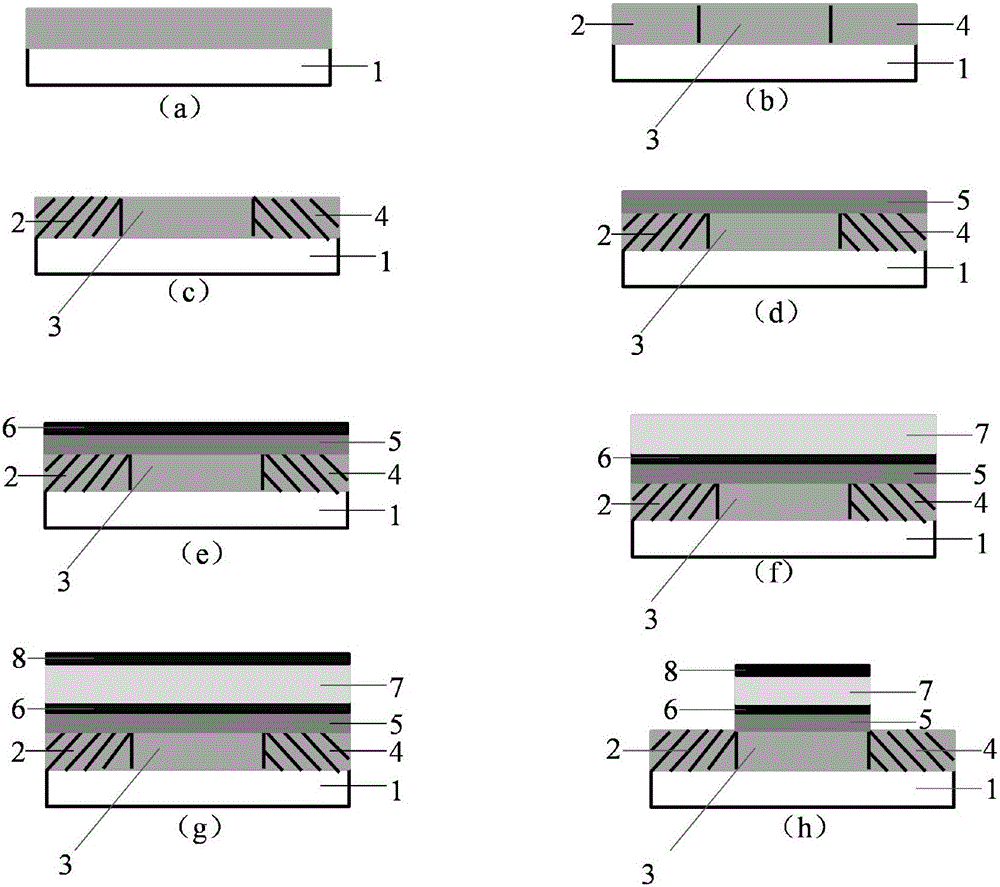

[0057] Using low-temperature solid-source molecular beam epitaxy, epitaxially grow 80nm Ge on undoped Ge substrates with high-purity Ge and Sn sources at 180°C 0.935 sn 0.065 layer. image 3 (a) For epitaxial growth of Ge 0.935 sn 0.065 Schematic diagram of the result after layers.

[0058] Step 2. Form the active layer by photolithography.

[0059] Using a 365nm I-line photolithography process, a source layer, a channel and a drain layer are formed on the GeSn layer, wherein the channel is located in the center of the GeSn layer, and the source layer and drain layer are located on both sides of the channel. image 3 (b) is a schematic diagram of the result after forming the source layer, channel and drain layer.

[0060] Step 3. Doping to form a source region and a drain region.

[0061] The implant energy in the source and drain...

Embodiment example 2

[0072] Implementation Case 2: Making Ge 0.935 sn 0.065 N-type ferroelectric field effect crystal.

[0073] Step 1. Epitaxial growth of a GeSn layer.

[0074] Using low-temperature solid-source molecular beam epitaxy, epitaxially grow 80nm Ge on undoped Ge substrates with high-purity Ge and Sn sources at 180°C 0.935 sn 0.065 layer. image 3 (a) For epitaxial growth of Ge 0.935 sn 0.065 Schematic diagram of the result after layers.

[0075] Step 2. Forming an active layer by photolithography.

[0076] Using a 365nm I-line photolithography process, a source layer, a channel and a drain layer are formed on the GeSn layer, wherein the channel is located in the center of the GeSn layer, and the source layer and drain layer are located on both sides of the channel. image 3 (b) is a schematic diagram of the result after forming the source layer, channel and drain layer.

[0077] Step 3. Doping to form a source region and a drain region.

[0078] The implantation energy in t...

Embodiment example 3

[0089] Implementation Case 3: Making Ge 0.9 sn 0.1 P-type ferroelectric field effect crystal.

[0090] Step a. epitaxially growing a GeSn layer.

[0091] Using low-temperature solid-source molecular beam epitaxy, epitaxially grow 80nm Ge on undoped Ge substrates with high-purity Ge and Sn sources at 180°C 0.9 sn 0.1 layer. image 3 (a) For epitaxial growth of Ge 0.9 sn 0.1 Schematic diagram of the result after layers.

[0092] Step b. Forming the active layer by photolithography.

[0093] Using a 365nm I-line photolithography process, a source layer, a channel and a drain layer are formed on the GeSn layer, wherein the channel is located in the center of the GeSn layer, and the source layer and drain layer are located on both sides of the channel. image 3 (b) is a schematic diagram of the result after forming the source layer, channel and drain layer.

[0094]Step c. Doping to form a source region and a drain region.

[0095] The implant energy in the source and dra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More