Parameter extraction method for small-signal circuit model of gallium nitride high electron mobility transistor

A high electron mobility and circuit model technology, applied in the field of microelectronics, can solve problems such as device damage, extraction of parasitic inductance, resistance error, and dependence, and achieve the effects of improving reference efficiency, applicable frequency bandwidth, and reducing errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] The principles and features of the present invention are described below in conjunction with the accompanying drawings, and the examples given are only used to explain the present invention, and are not intended to limit the scope of the present invention.

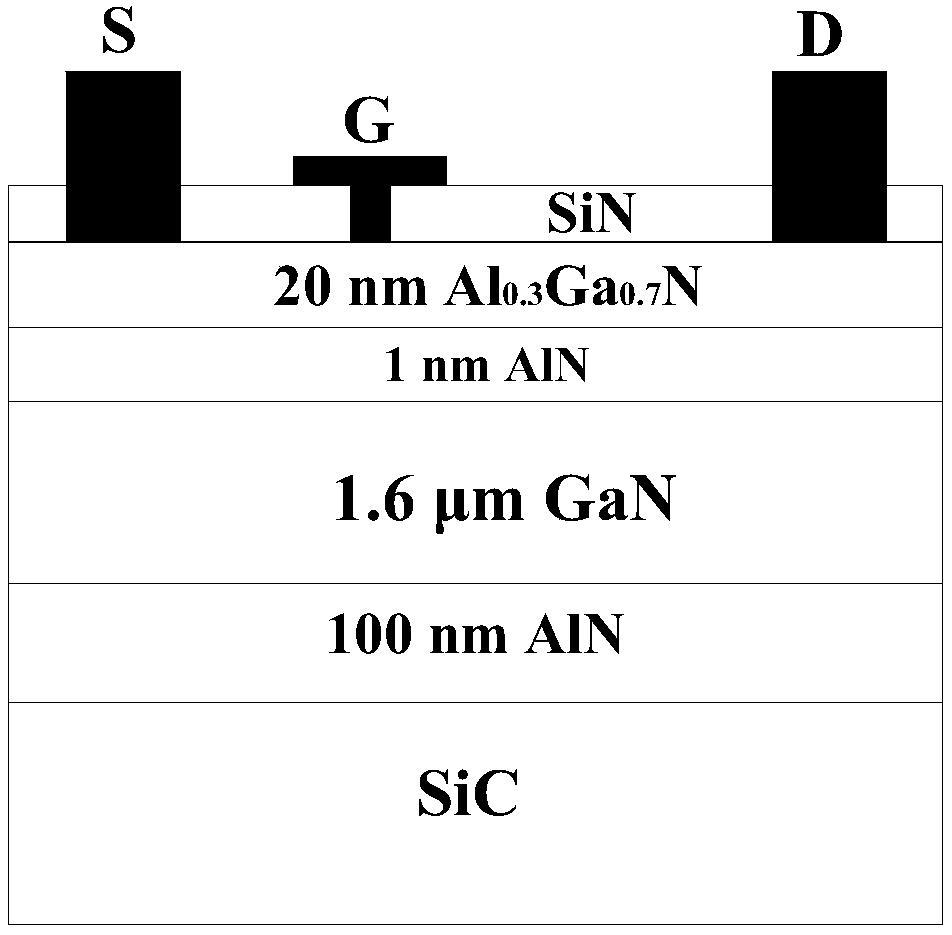

[0041] refer to figure 1 , the existing GaN HEMT device consists of a 2-inch 4H-SiC substrate from bottom to top, a 100nm thick AlN nucleation layer, a 1.6um thick GaN buffer layer, a 1nm AlN insertion layer, and a 20nm undoped AlGaN barrier layer, 60nm SiN passivation layer, Ti / Al / Ni / Au ohmic source electrode and ohmic drain electrode and Ni / Au / Ni Schottky gate, the gate width of the device is 10x125um, the gate length is 0.4um, gate-gate , Gate-source, gate-drain spacing are 40um, 0.7um and 2.8um respectively.

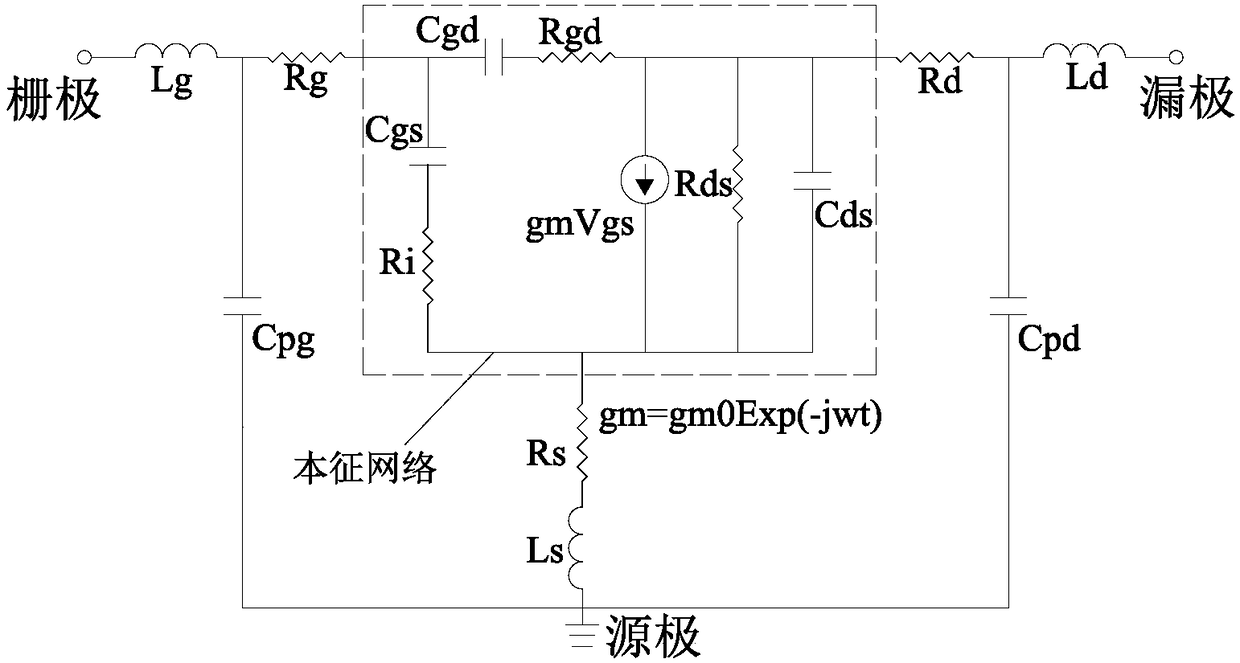

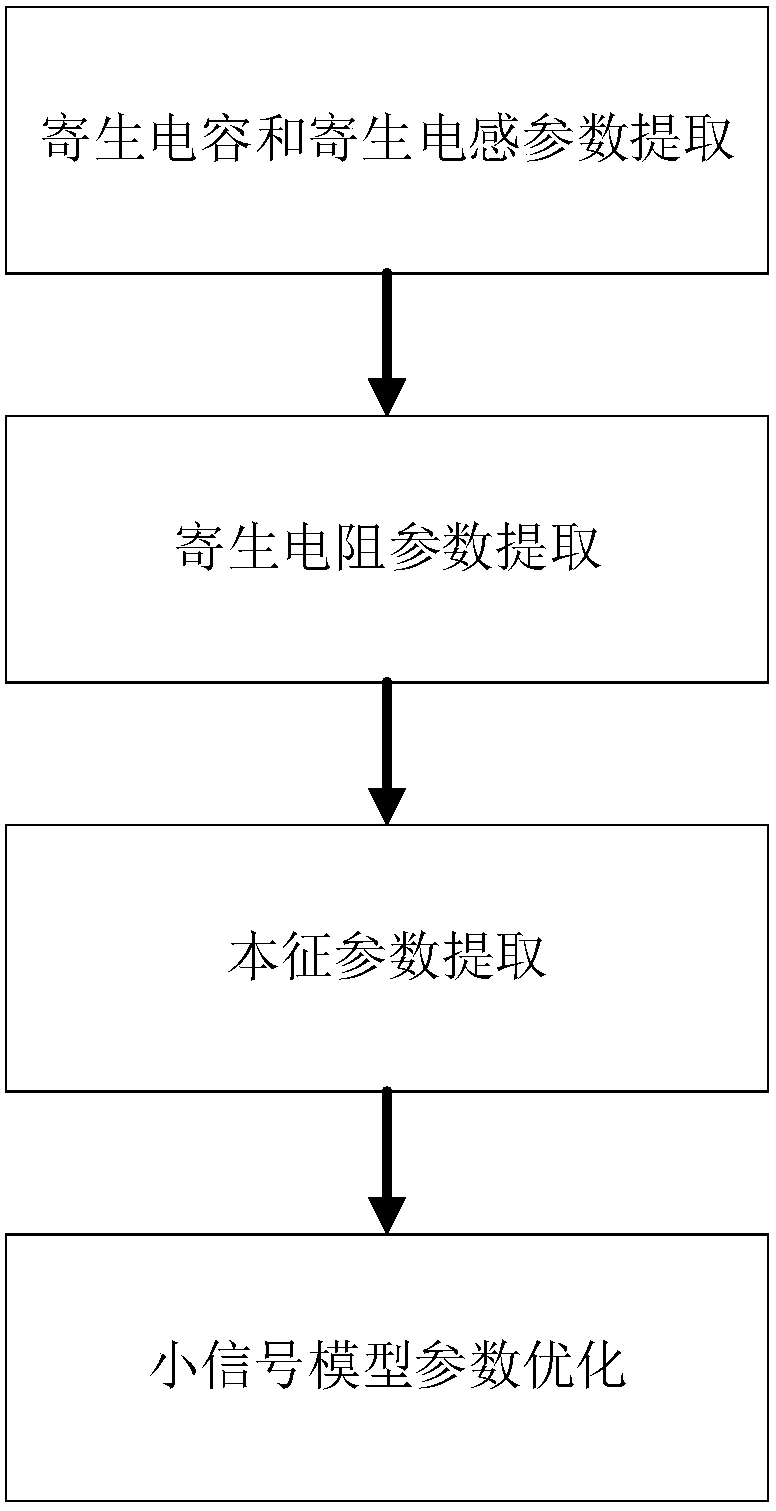

[0042] figure 1 The small-signal equivalent circuit diagram of the device structure shown is figure 2 As shown, it includes 16 circuit components, which are divided into two categories, namely peripher...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More