Semiconductor device and preparation method thereof and electronic device

A technology for semiconductors and devices, applied in the field of semiconductor manufacturing, can solve problems such as failure, device performance and yield reduction, sidewall damage, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

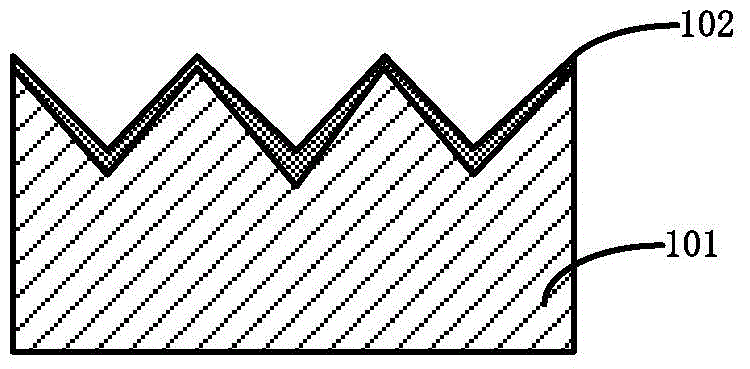

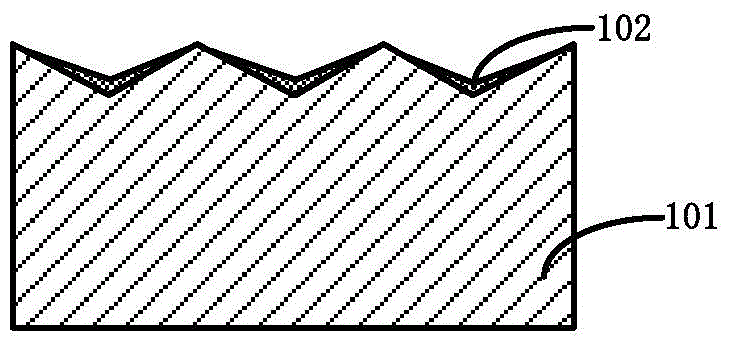

[0040]The current manufacturing method of the semiconductor device includes the following steps: firstly providing a semiconductor substrate, forming a floating gate material layer and a hard mask layer on the semiconductor substrate, then patterning the hard mask layer (HMetch), and Etching the floating gate material layer using the hard mask layer as a mask to form a floating gate structure, then depositing an ALD oxide layer to form an oxide layer on the sidewall of the floating gate structure, and then using the The hard mask layer and the floating gate structure are used as masks to etch the semiconductor substrate to form shallow trenches in the semiconductor substrate, and then the shallow trench isolation materials are selected to fill the shallow trenches and planarized to form a shallow trench isolation structure, and then remove the hard mask layer, and then perform a step of opening (cellopen, COPEN) a memory cell to remove part of the oxide in the shallow trench is...

Embodiment 1

[0043] In order to solve the problems existing in the prior art, the present invention improves the manufacturing process steps of the semiconductor device and the parameters in the steps, so as to eliminate the above-mentioned problems, the preparation method of the semiconductor device of the present invention is further described below illustrate.

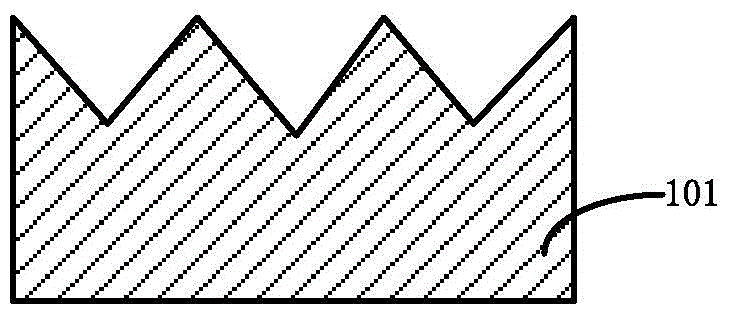

[0044] First, step 201 is performed to provide a semiconductor substrate, on which a floating gate material layer and a hard mask layer are sequentially formed.

[0045] Specifically, wherein, the semiconductor substrate may be at least one of the materials mentioned below: silicon, silicon-on-insulator (SOI), silicon-on-insulator (SSOI), silicon-germanium-on-insulator (S- SiGeOI), silicon germanium on insulator (SiGeOI) and germanium on insulator (GeOI), etc.

[0046] A floating gate material layer and a mask layer are formed on the semiconductor substrate and patterned to form a floating gate structure and a shallow trench. ...

Embodiment 2

[0091] The present invention also provides a semiconductor device, which is prepared by the method described in Embodiment 1. The sidewall of the floating gate structure in the semiconductor device prepared by the method of the present invention is not damaged, and the sidewall of the floating gate structure is smoother, which improves the coupling performance with the subsequently formed control gate structure, and further Improve device performance and yield.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More