Grooved PCB structure used for bare chip testing and manufacturing method thereof

A PCB board, bare chip technology, applied in the field of semiconductor integrated circuit testing, can solve the problems of metal PAD short circuit, conductive glue overflow, bare chip scrapping, etc., to avoid pollution, facilitate bonding, and avoid precision control problems.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The present invention will be further described below in conjunction with the accompanying drawings and embodiments, and the present invention includes but not limited to the following embodiments.

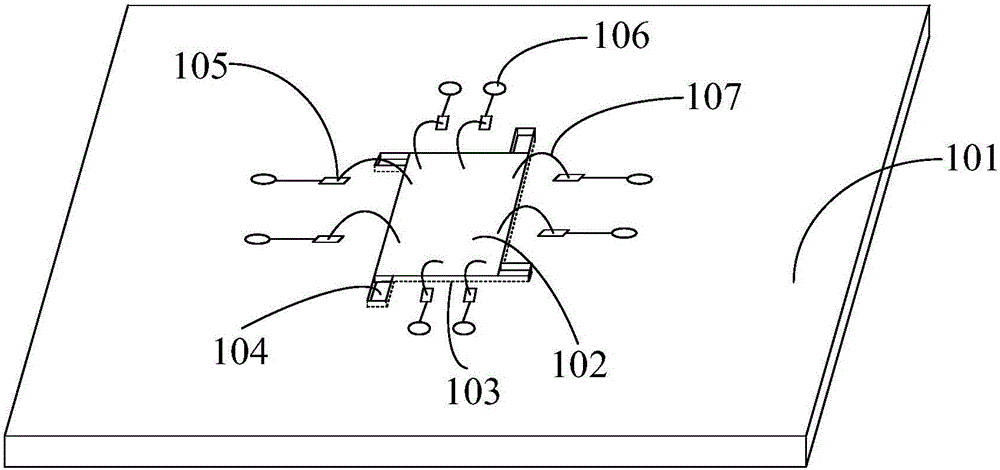

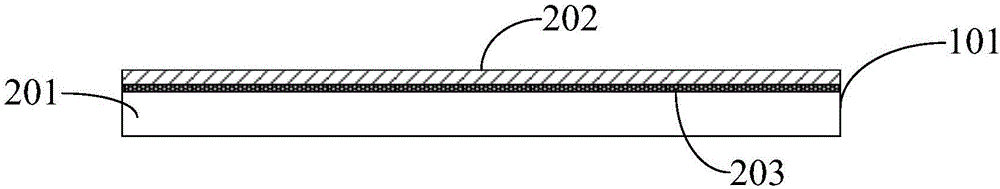

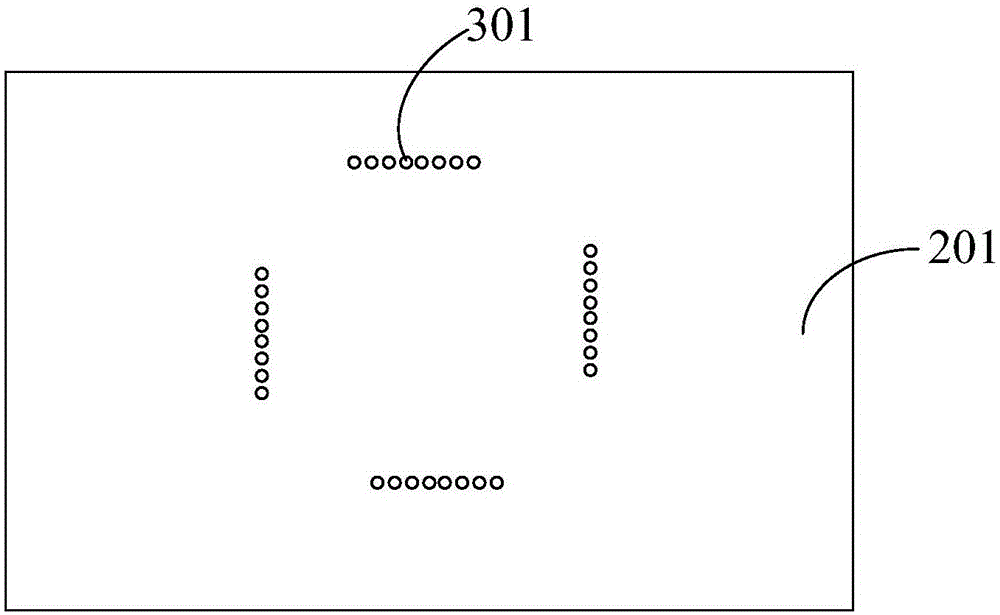

[0019] Such as figure 1 As shown, the present invention is composed of a PCB board 101 , a bare chip 102 , a groove 103 , an ear structure 104 , a metal pad 105 , a connection through hole 106 , and a bonding wire 107 . Such as figure 2 As shown, the PCB board 101 is composed of a first PCB board 201, a second PCB board 202, and an insulating medium layer 203. The insulating medium layer 203 is used for bonding between the first PCB board 201 and the second PCB board 202, while avoiding the first PCB board 201 and the second PCB board 202. The electrical short circuit between the first PCB board 201 and the second PCB board 202 . Such as image 3 As shown, the first PCB 201 is provided with a through-hole copper avoidance area 301, which is used to avoid the metal groun...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More