Wafer packaging structure for infrared focal plane array

A wafer-level packaging, infrared focal plane technology, applied in microstructure technology, microstructure devices, manufacturing microstructure devices, etc., can solve the problems of bulky structure, high cost, low assembly efficiency, etc., and achieve small size and cost. low effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

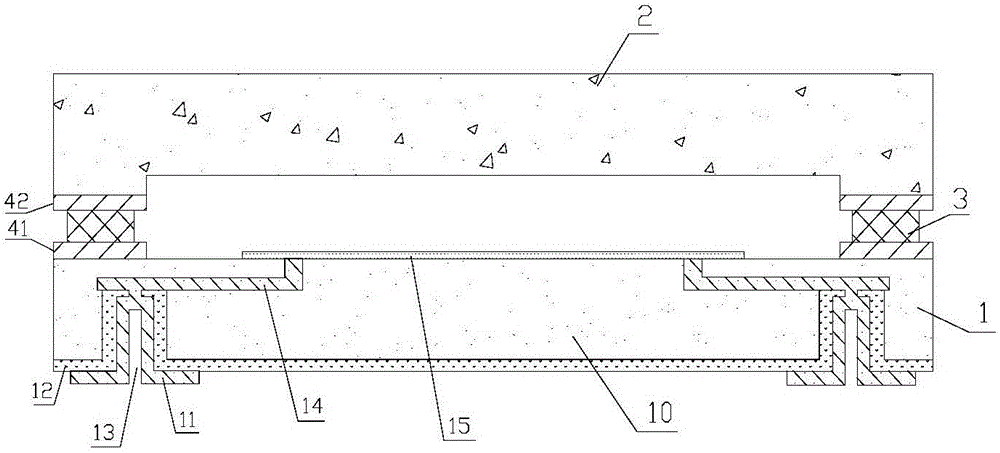

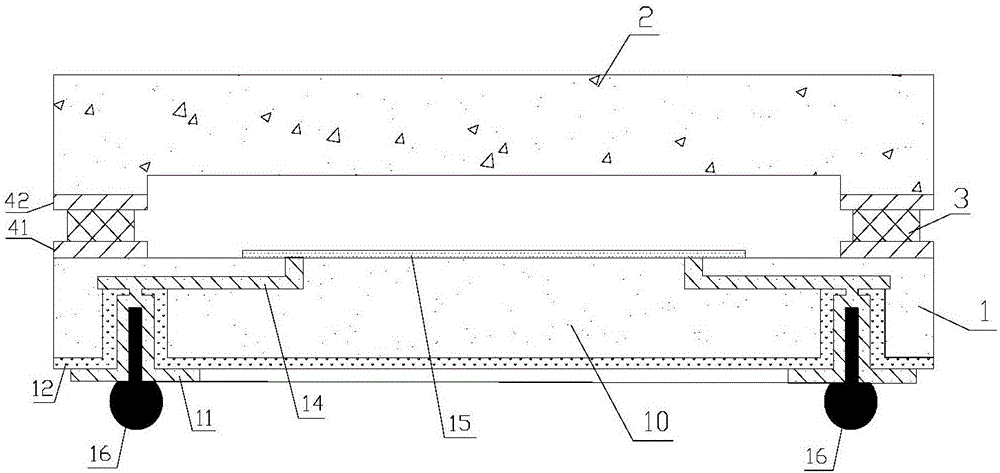

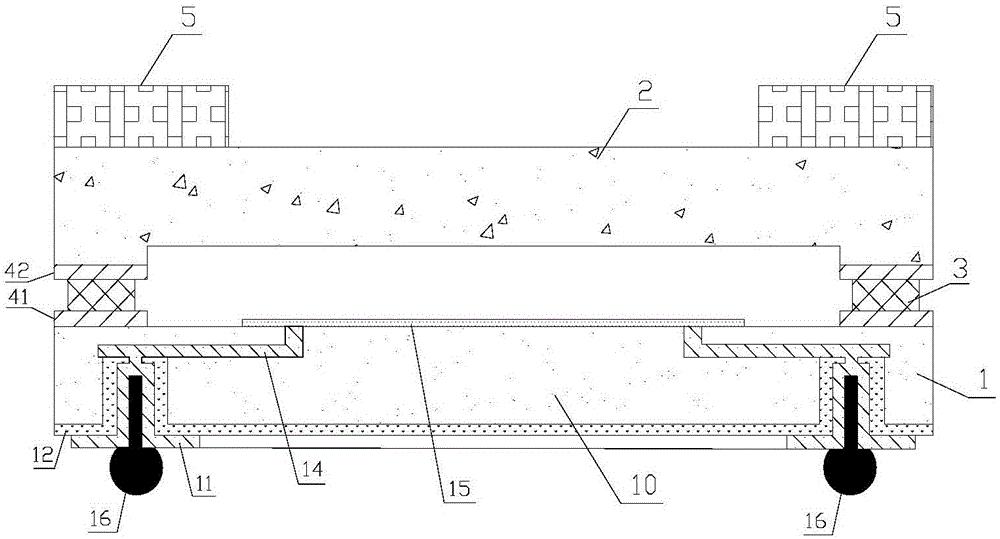

[0031] This embodiment proposes a wafer-level packaging structure of an infrared focal plane array, such as Figure 1 to Figure 4 As shown, it mainly includes:

[0032] An infrared detector chip 1, on which an infrared focal plane array 15 is arranged;

[0033] The infrared light window 2 is arranged on the infrared detector chip 1, and the edge of the infrared light window 2 is sealed and connected with the edge of the infrared detector chip 1, so as to form a vacuum chamber in which the vacuum air is sealed and connected to the infrared focal plane array 15;

[0034] The lens 6 is arranged above the infrared light window 2 , and the edge of the lens 6 is sealed and connected with the edge of the infrared light window 2 .

[0035] On the basis of the above technical solution, as a preferred implementation mode, this embodiment uses an oxygen-free silicon wafer as the infrared window 2, and on both sides of the oxygen-free silicon wafer (ie, the infrared window 2), a An infr...

Embodiment 2

[0050] This embodiment proposes a packaging method for infrared focal plane arrays, based on the wafer-level packaging structure of Embodiment 1, such as Figure 1 to Figure 4 As shown, it mainly includes:

[0051] first step, such as figure 1 As shown, the edge of the silicon light window 2 and the edge of the infrared detector chip 1 are bonded by gold-tin eutectic solder 3 to form a vacuum cavity, and the conductive leads 14 of the infrared detector chip 1 are buried in the infrared detector chip 1. internal.

[0052] The second step, such as figure 2As shown, after thinning the second surface of the infrared detector chip 1 (that is, the lower surface in the figure), a deep hole 13 is opened on the second surface, and a passivation layer 12 and a metal layer are formed in the deep hole 13. The layer 11 and the passivation layer 12 serve as an insulating layer for electrical connection to insulate the metal layer 11 from the silicon substrate 10 , while the metal layer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More