GaN transistor and manufacturing method thereof

A technology of transistors and gallium nitride, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as poor device performance and large ohmic contact resistance, increase device current, reduce ohmic contact resistance, The effect of improving overall performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

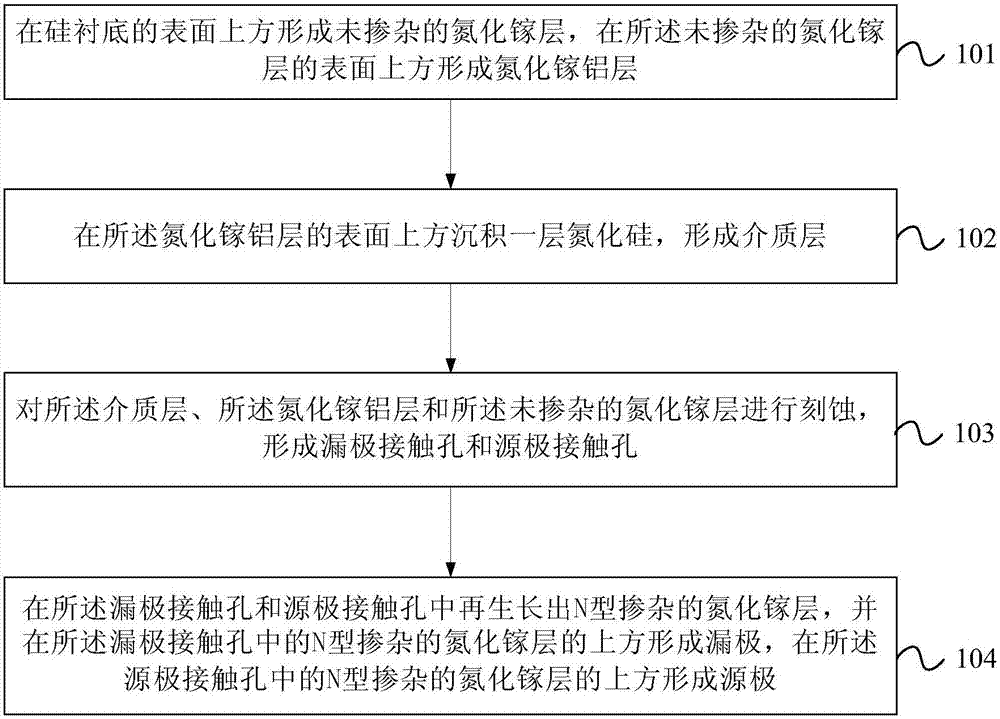

[0058] Embodiment 1 of the present invention provides a method for manufacturing a gallium nitride transistor. figure 1 It is a flowchart of a method for manufacturing a gallium nitride transistor provided in Embodiment 1 of the present invention. Such as figure 1 As shown, the method in this embodiment may include:

[0059] Step 101 , forming an undoped gallium nitride layer 2 on the surface of the silicon substrate 1 , and forming an aluminum gallium nitride layer 3 on the surface of the undoped gallium nitride layer 2 .

[0060] Step 102 , depositing a layer of silicon nitride on the surface of the aluminum gallium nitride layer 3 to form a dielectric layer 4 .

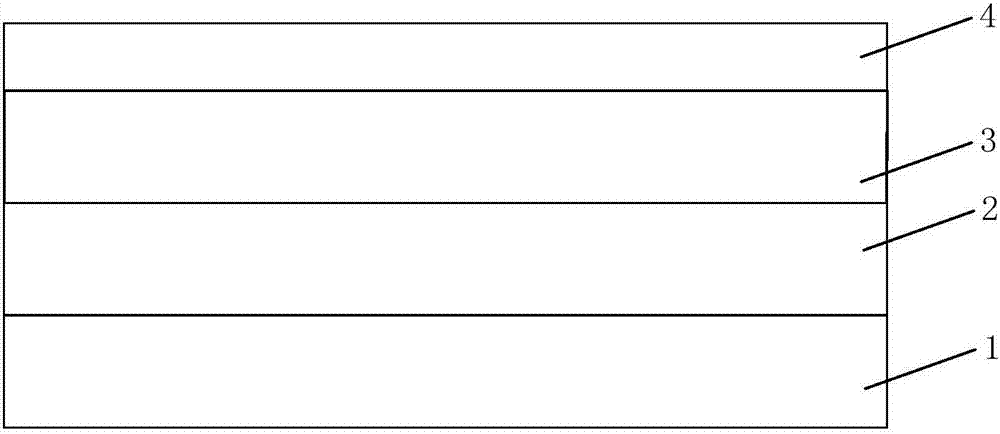

[0061] figure 2 It is a schematic diagram of the device structure after the dielectric layer 4 is formed in the GaN transistor manufacturing method provided in Embodiment 1 of the present invention.

[0062] Such as figure 2 As shown, a layer of gallium nitride can be deposited on the surface of the silicon su...

Embodiment 2

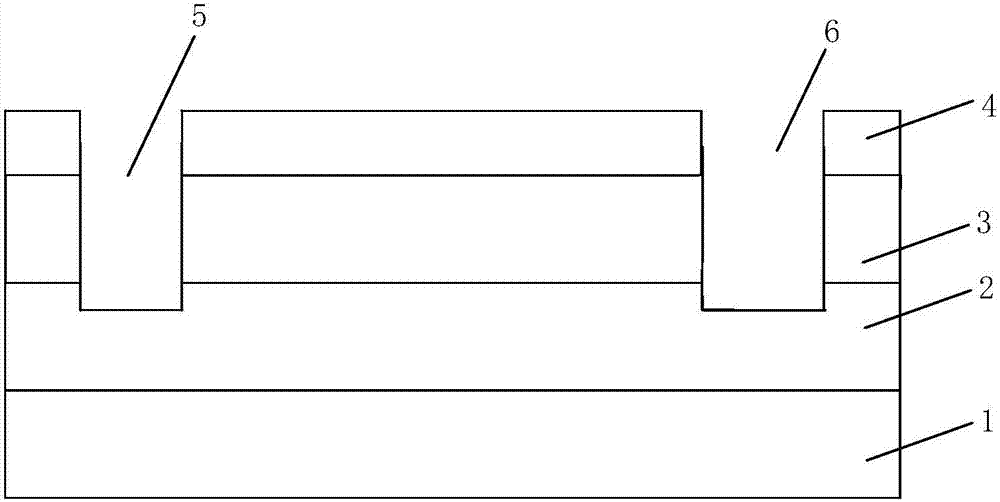

[0096] Embodiment 2 of the present invention provides a gallium nitride transistor. The specific structure of the gallium nitride transistor provided in this embodiment can refer to Figure 9 . Such as Figure 9 As shown, the gallium nitride transistor in this embodiment may include:

[0097] A silicon substrate 1, an undoped gallium nitride layer 2 arranged above the silicon substrate 1, an aluminum gallium nitride layer 3 arranged above the undoped gallium nitride layer, and an aluminum gallium nitride layer arranged on the said undoped gallium nitride layer a dielectric layer 4 above the aluminum gallium nitride layer 3;

[0098] A source contact hole 6 and a drain contact hole 5 are opened in the dielectric layer 4, and both the source contact hole 6 and the drain contact hole 5 pass through the aluminum gallium nitride layer 3 and pass through Part of said undoped gallium nitride layer 2;

[0099] An N-type doped gallium nitride layer 7 is formed in the drain contact...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com