Three-dimensional through silicon via vertical interconnection method based on multi-layer graphene auxiliary layer

A multi-layer graphene and auxiliary layer technology, which is applied in the manufacturing of electrical components, electrical solid-state devices, semiconductor/solid-state devices, etc. performance and reliability, improving the effect of signal fidelity transmission

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

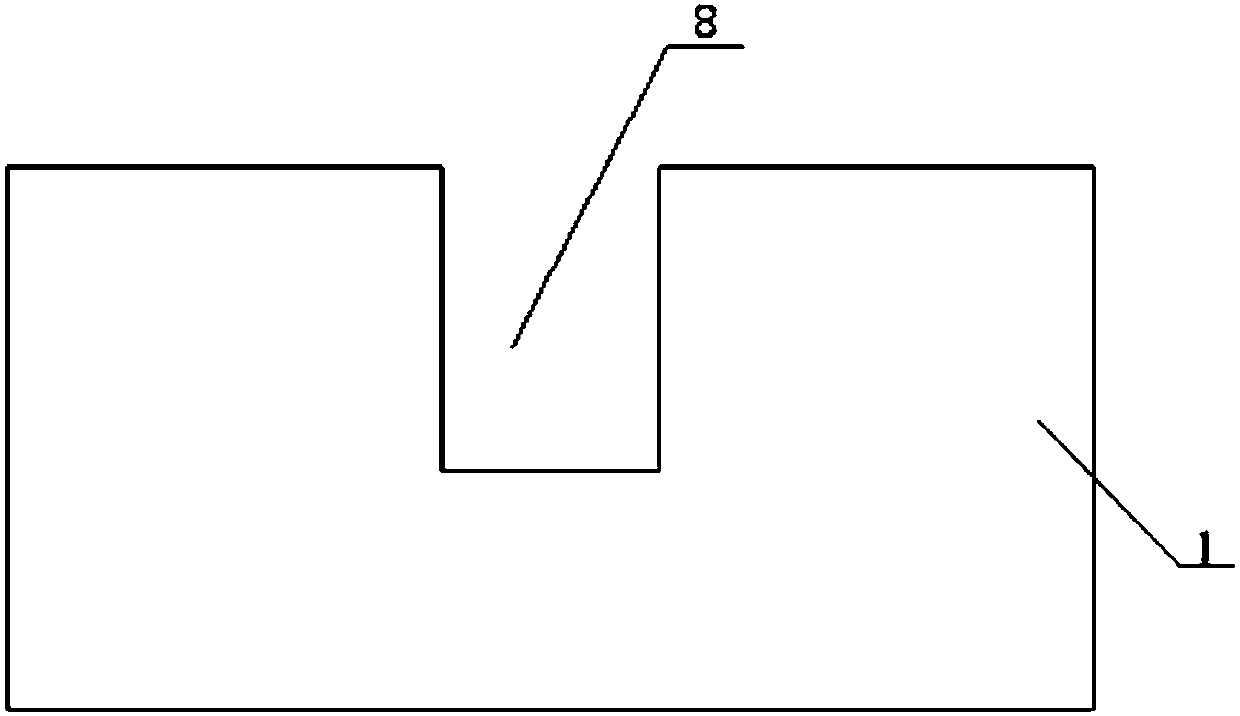

[0039] Such as figure 1 As shown, the silicon hole 8 is made on the silicon substrate 1 by deep reactive ion etching, laser etching or wet etching; the diameter of the silicon hole 8 is 1 micron to 100 microns, and the cross section of the silicon hole 8 is generally The silicon hole 8 is circular, and the aspect ratio of the silicon hole 8 is generally 1-30.

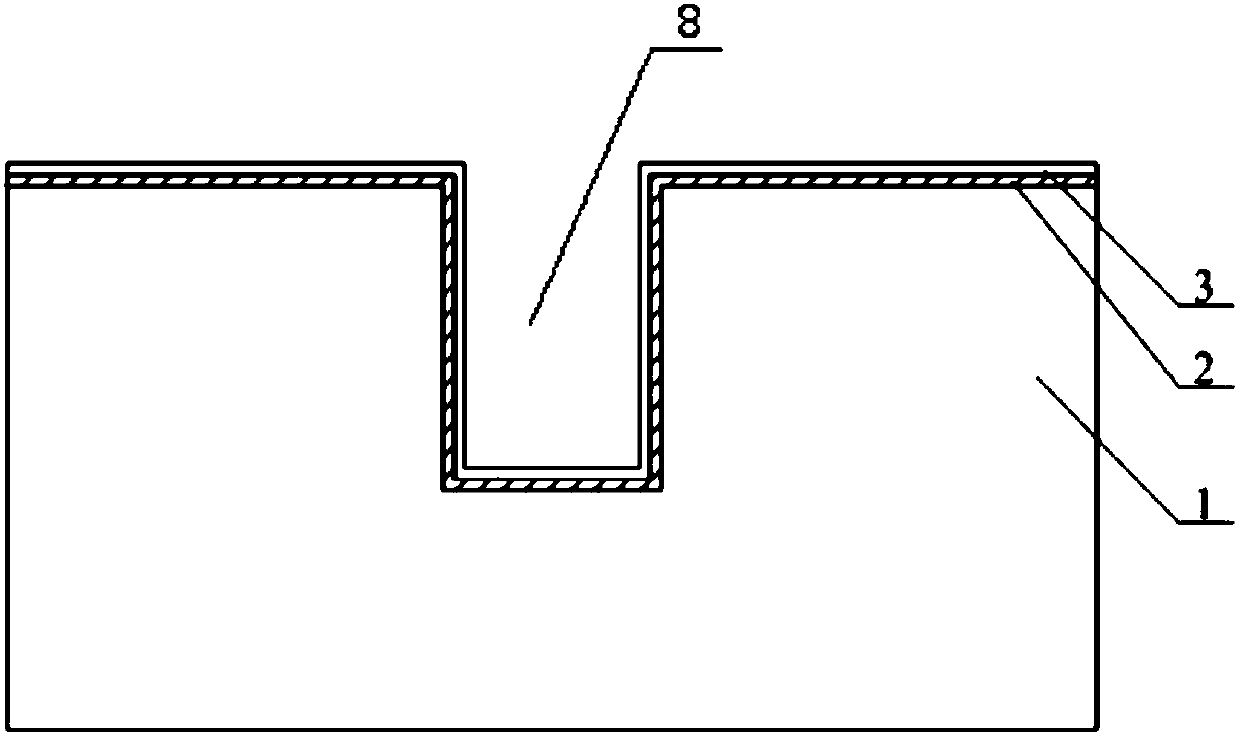

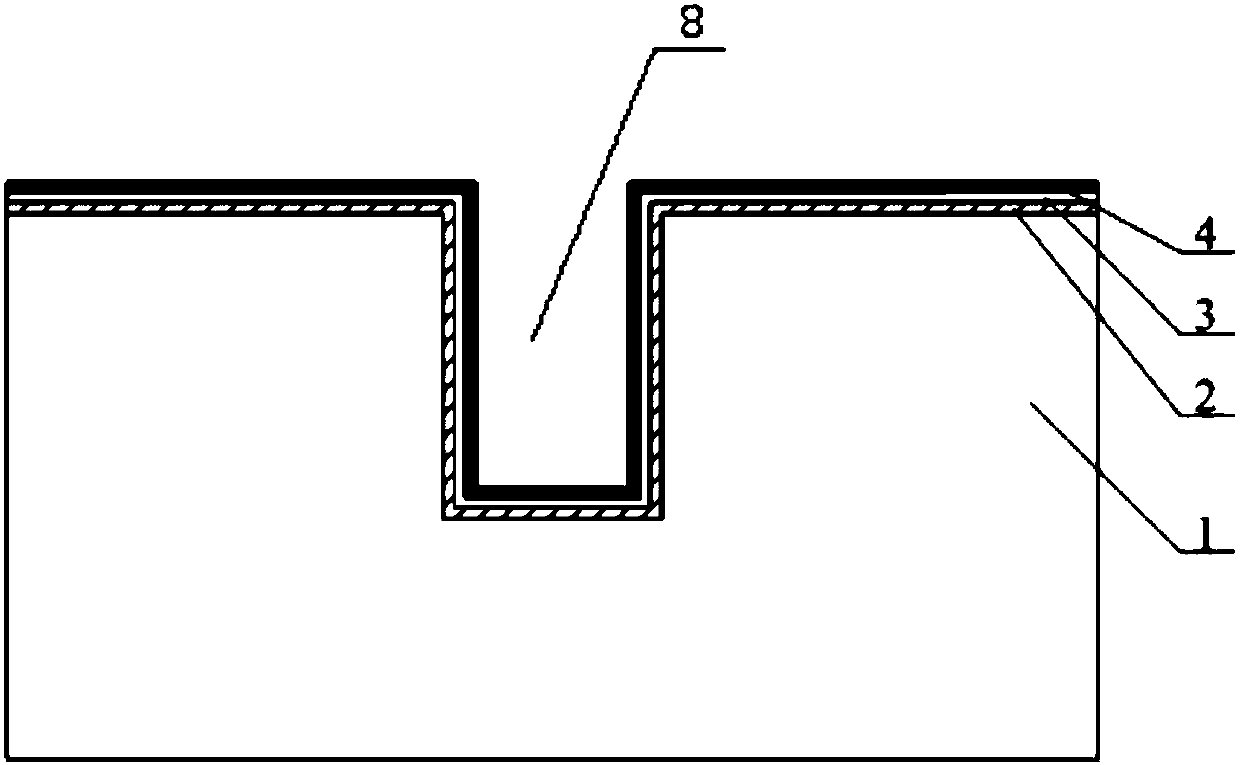

[0040] Such as figure 2 As shown, an insulating layer 2 is deposited on the surface of the silicon substrate 1 and the inner wall (circumferential surface and bottom surface) of the silicon hole 8. The deposition of the insulating layer 2 is made by thermal oxidation, chemical vapor deposition or physical vapor deposition. The material of the insulating layer 2 Silicon dioxide, alumina, etc., polyimide, parylene, etc. can be used, and the thickness of the insulating layer 2 is 0.5 to 1 micron; a barrier layer 3 is deposited on the insulating layer 2, and the barrier layer 3 is magnetron sputtered , physical vapor dep...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com