Display panel, manufacturing method thereof, and display device

A technology for a display panel and a manufacturing method, applied in the field of display panels and display devices, capable of solving problems such as poor display performance and damage to a planarization layer, and achieving the effects of avoiding poor display performance, uniform thickness, and guaranteed thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

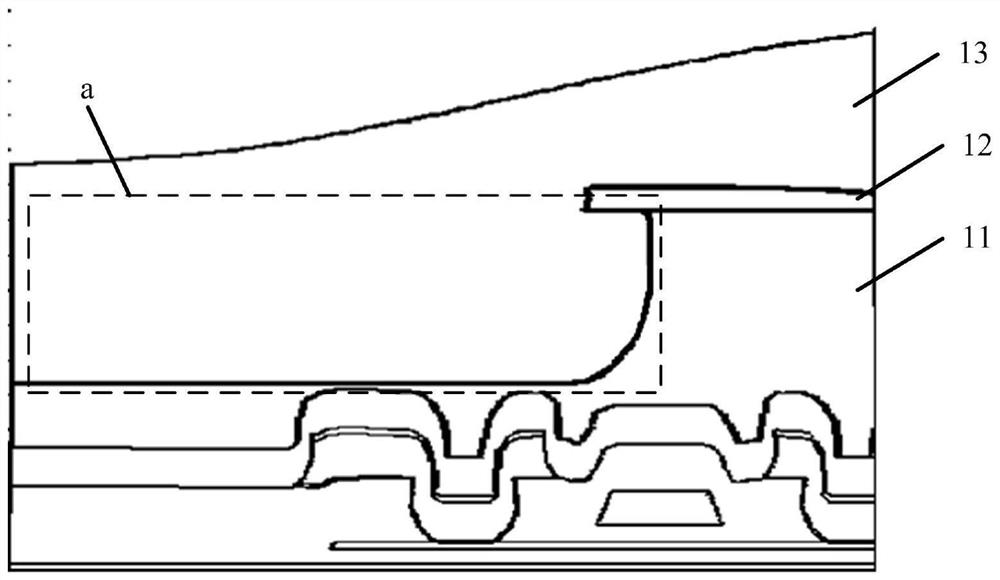

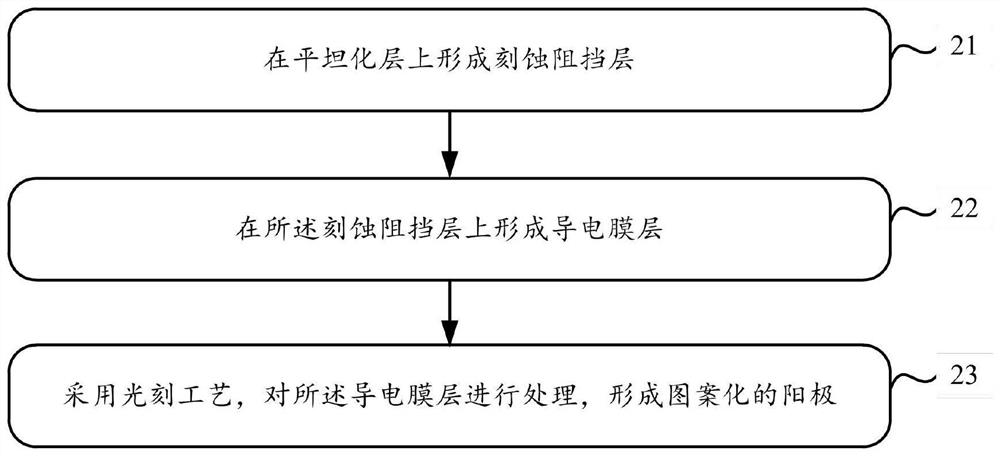

[0041] An embodiment of the present application provides a method for fabricating a display panel, and the flow chart of the method is as follows figure 2 As shown, this method is used to solve the problem that the flattening layer is damaged during the anode etching process, resulting in poor display performance. The above-mentioned poor display performance is mainly due to the fact that the planarization layer is destroyed during the anode etching process, so that the overall thickness of the pixel definition layer formed on the planarization layer is uneven. Then in the process of evaporating the light-emitting layer, there is a gap between the reticle and the pixel definition layer covered by the reticle, so that the light-emitting layer is also evaporated in the pixel definition layer at the position covered by the reticle, resulting in an inaccurate evaporation position of the light-emitting layer. Affects the glow effect of the emissive layer. The method provided by t...

Embodiment 2

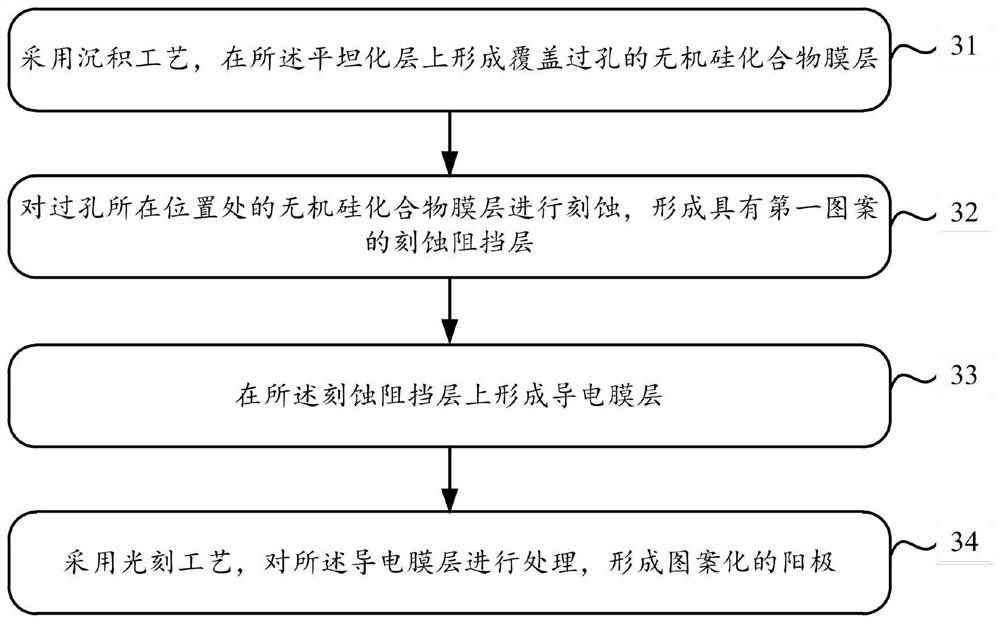

[0052] Based on the above-mentioned embodiments, this embodiment provides a better method for manufacturing a display panel. The method flow is as follows image 3 shown, including the following steps:

[0053] Step 31: Using a deposition process, an inorganic silicon compound film layer covering the via holes is formed on the planarization layer;

[0054] Specifically, the material of the inorganic silicon compound film layer can be silicon oxide or silicon nitride, and the film layer can be deposited on the flattening layer by means of low-temperature chemical vapor deposition, which can cover the flattening layer and the excess in the flattening layer. hole location.

[0055] Step 32 : etching the inorganic silicon compound film layer at the position of the via hole to form an etching barrier layer with a first pattern.

[0056] Since the inorganic silicon compound film layer does not have good electrical conductivity and covers the via hole position in the planarization ...

Embodiment 3

[0065] Based on the above embodiment, this embodiment provides another preferred method for manufacturing a display panel. The method flow is as follows Figure 4 shown, including the following steps:

[0066] Step 41: Using a deposition process, a metal film layer covering the via holes is formed on the planarization layer as an etching barrier layer.

[0067] Specifically, the material of the metal film layer can be an inert metal such as titanium or molybdenum, and the film layer can be deposited on the planarization layer by means of physical vapor deposition, which can cover the planarization layer and the via positions in the planarization layer.

[0068] Since the metal film layer has a certain conductivity, the metal film layer covering the via position will not significantly affect the signal transmission between the transmission line and the anode layer under the planarization layer. Therefore, there is no need to change the position of the via hole The metal film l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More