CPU+FPGA-based heterogeneous computing system and acceleration method thereof

A computing system and heterogeneous technology, applied in the field of heterogeneous computing, can solve the problems of unable to meet the computing needs of large-scale computing tasks, limited acceleration capabilities, and limited acceleration performance, so as to shorten execution time, improve throughput, and improve computing performance effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

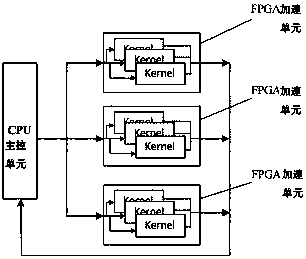

[0035] The present embodiment proposes a heterogeneous computing system based on CPU+FPGA, and the CPU+FPGA heterogeneous computing system uses the OpenCL programming model for programming; its system architecture includes: a CPU main control unit and several FPGA acceleration units; the FPGA acceleration unit Interconnect and communicate with the CPU main control unit through the PCIe-DMA bus;

[0036] The CPU main control unit is responsible for logic judgment, management control, and allocates calculation tasks to the FPGA acceleration unit; the FPGA acceleration unit is provided with multiple, responsible for accelerating the calculation task; between a plurality of FPGA acceleration units, the SRIO bus is used Internet communication;

[0037] The FPGA acceleration unit is internally divided into two parts, a static area and a dynamic reconfigurable area; the static area is responsible for realizing functions such as PCIe-DMA communication, SRIO communication, and a DDR co...

Embodiment 2

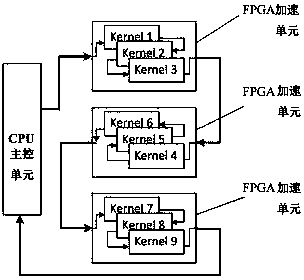

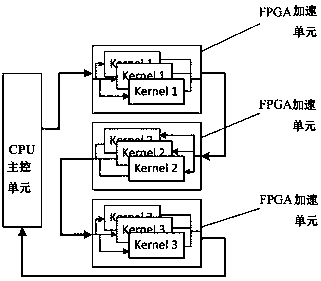

[0045] A heterogeneous computing system based on CPU+FPGA proposed in this embodiment is another specific implementation of the present invention. On the basis of the heterogeneous computing system based on CPU+FPGA in Embodiment 1, in order to meet the requirements of different types of computing tasks , the FPGA acceleration unit is configured into multiple acceleration modes, including: parallel acceleration mode, pipeline acceleration mode, pipeline and parallel hybrid acceleration mode; realizing parallel acceleration processing and pipeline acceleration processing of computing tasks, which can greatly improve the throughput of task processing Rate.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More