Method for detecting voids in dielectric layer and method for manufacturing semiconductor device

A dielectric layer, void detection technology, applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device testing/measurement, electrical components, etc., can solve the problems of increased R&D costs, limited number of samples, small gaps, etc., to save cost, improved deposition performance, avoided effects of time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

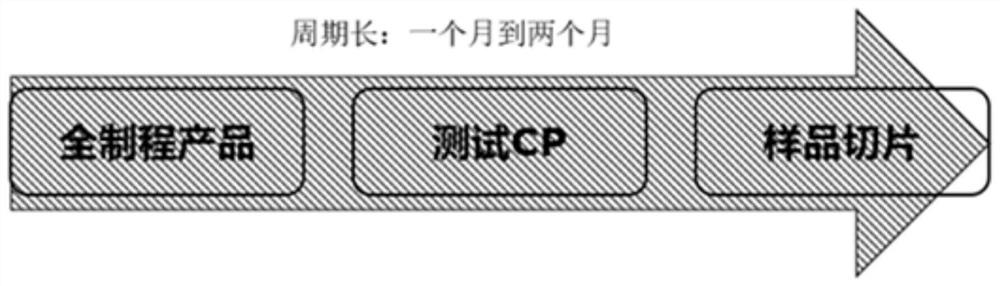

[0048] As mentioned in the background technology, in the prior art, for the detection of voids in the dielectric layer, it is necessary to perform CP test on the full-process product after obtaining the full-process product, and then further perform sample slicing for failure analysis, such as Figure 1b As shown, this method has a long cycle, high cost, and is difficult to quantify.

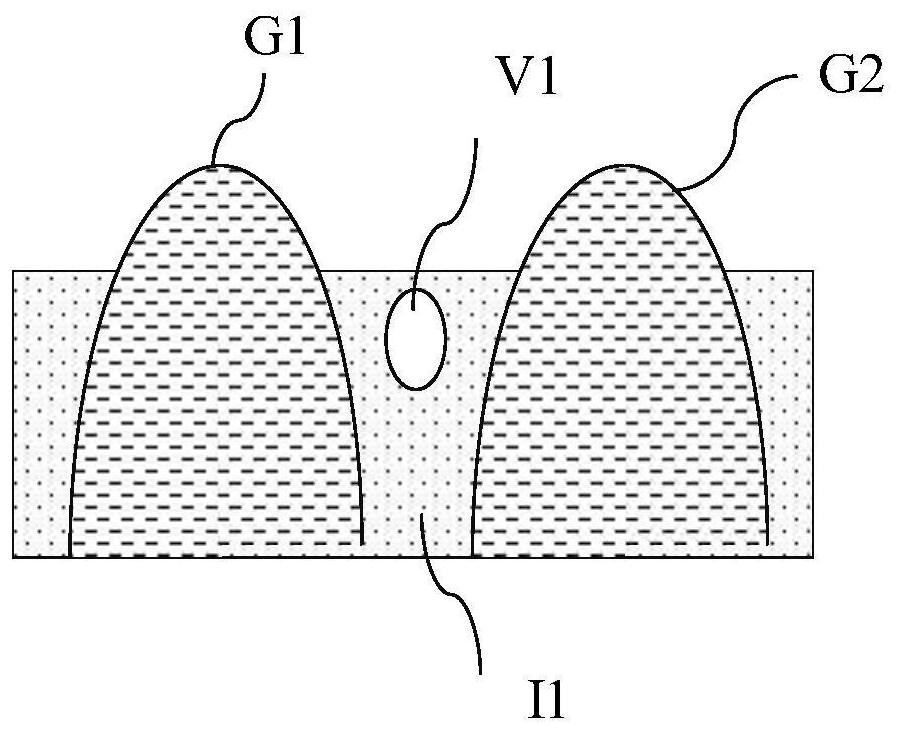

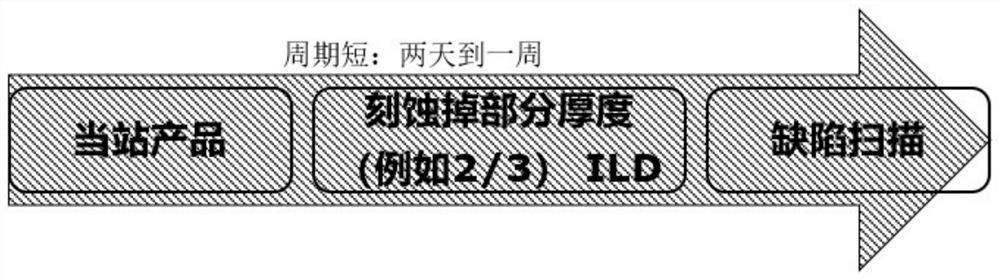

[0049] Based on this, the present invention provides a method for detecting voids in dielectric layers, please refer to Figure 2a , the detection of voids in the dielectric layer is carried out at the local station, that is, after the current station product is obtained, the dielectric layer of the current station product is first etched and thinned, exposing the corresponding part of the conductive contact plug. According to the stronger optical signal of the conductive contact plug, the position where the side wall of the conductive contact plug is bridged is easier to be found by the defect ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com