Double-gate thin film transistor, sensor and manufacturing method

A thin-film transistor and sensing layer technology, which is applied in the field of electronic sensing, can solve problems affecting the integration and thinness of sensors, and achieve the effects of small size, enhanced effective voltage, and high sensitivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

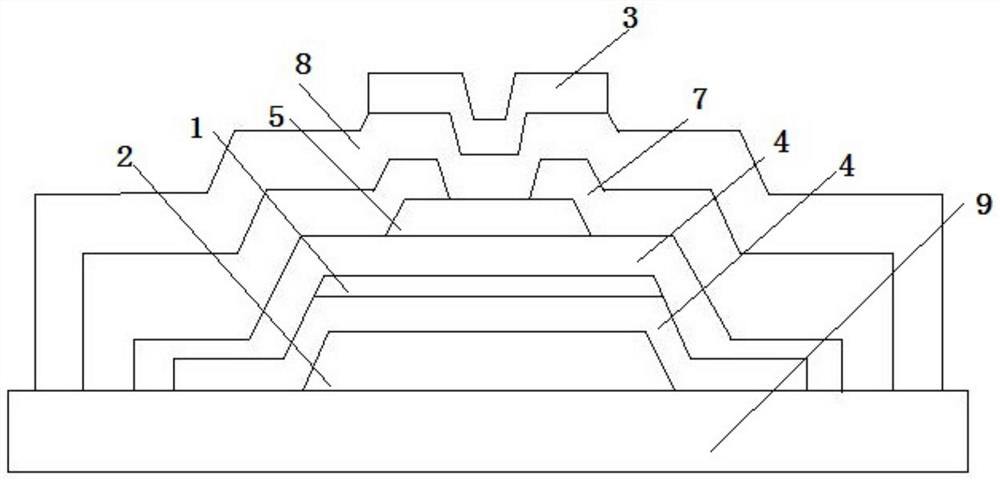

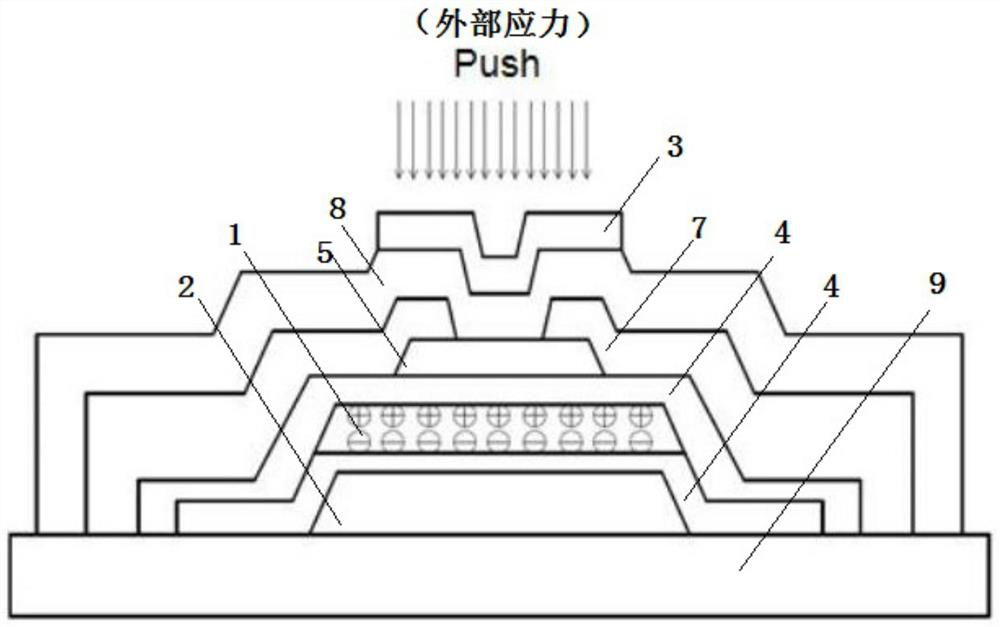

[0043] Reference attached figure 1 , the dual-gate thin film transistor provided by the embodiment of the present invention includes a stress sensing layer 1, the stress sensing layer 1 is arranged between the bottom gate 2 and the top gate 3, and the stress sensing layer 1 and A bottom gate insulating layer 4 is provided between the bottom gate 2 and the top gate 3;

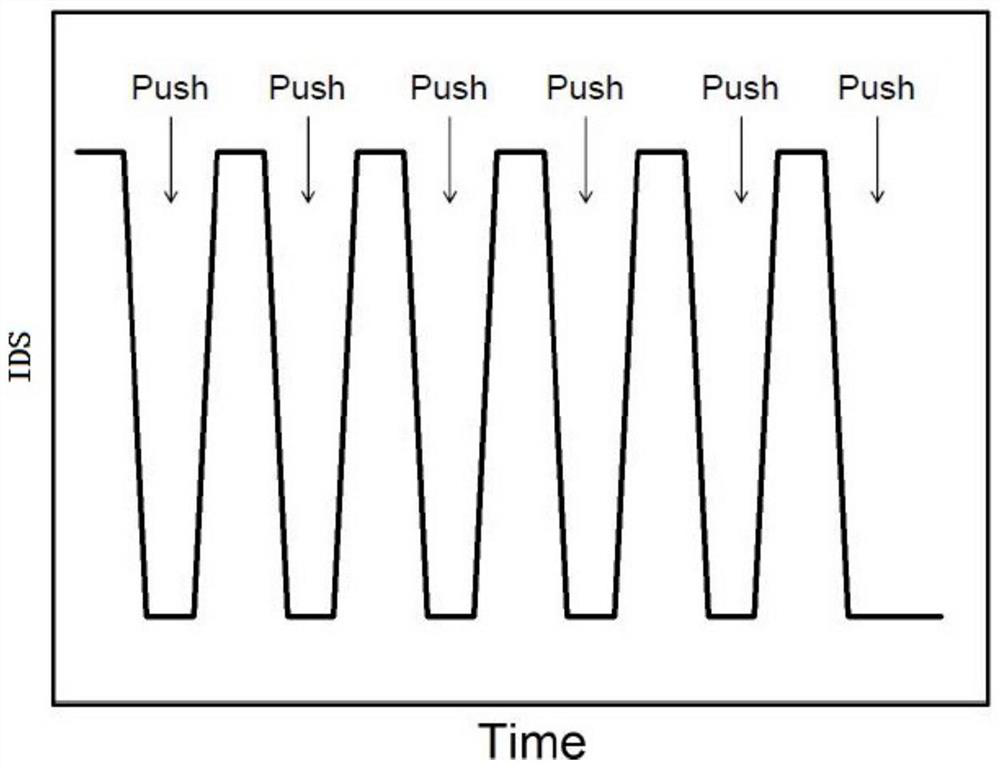

[0044] Wherein, a first preset voltage is applied to the bottom gate 2, a second preset voltage is applied to the top gate 3, the first preset voltage is greater than the second preset voltage, and the stress The sensing layer 1 forms a built-in electric field to reduce the effective gate voltage between the bottom gate 2 and the top gate 3, and the source-drain current is inversely proportional to the external pressure;

[0045] Or the first preset voltage is less than the second preset voltage, forming a built-in electric field in the stress sensing layer 1 to enhance the effective gate voltage between the bo...

Embodiment 2

[0058] Further, the embodiment of the present invention provides a double-gate thin film transistor, in a specific implementation, the stress sensing layer 1 includes a plurality of stress sensing units;

[0059] The stress sensing unit includes a piezoelectric material and a bottom gate insulating layer 4, and the bottom gate insulating layer 4 is respectively provided at the upper and lower ends of the piezoelectric material;

[0060] Wherein, the plurality of stress sensing units are stacked.

[0061] Specifically, in order to improve the sensitivity of the double-gate thin film transistor, in the technical solution adopted by the present invention, the stress sensing layer 1 is designed with a multi-layer structure, that is, the bottom gate insulating layer 4, the piezoelectric material, the bottom gate The insulating layer 4 is one layer, and the same structure is stacked in multiple layers, and both ends must be bottom gate insulating layers 4; two layers of bottom gate ...

Embodiment 3

[0066] Further, refer to the attached Figure 5 The method for manufacturing the double-gate thin film transistor described in the foregoing embodiments provided by the embodiments of the present invention includes the following steps:

[0067] S1, cleaning the substrate 9;

[0068] S2. Prepare the bottom gate 2 on the substrate 9 and perform patterning treatment on it. The material for making the bottom gate 2 can be metal conductive material and oxide conductive material;

[0069] S3. Prepare a bottom gate insulating layer 4 on the bottom gate 2, and pattern it. The material for making the bottom gate insulating layer 4 can be silicon nitride (SiN x ), alumina (Al 2 o 3 ) and silicon dioxide (SiO 2 ) and other insulating materials;

[0070] S4. Prepare a stress sensing layer 1 on the bottom gate insulating layer 4, and perform patterning on it. The orthographic projection of the stress sensing layer 1 should at least coincide with the bottom gate 2, so The stress sensi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More