Accelerator for GoogLeNet model and method thereof

An accelerator and model technology, applied in the field of neural network algorithms and optoelectronic computing, can solve the problems of gradient dispersion, high computational complexity, and difficulty in optimizing models, and achieve high energy efficiency and small size.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

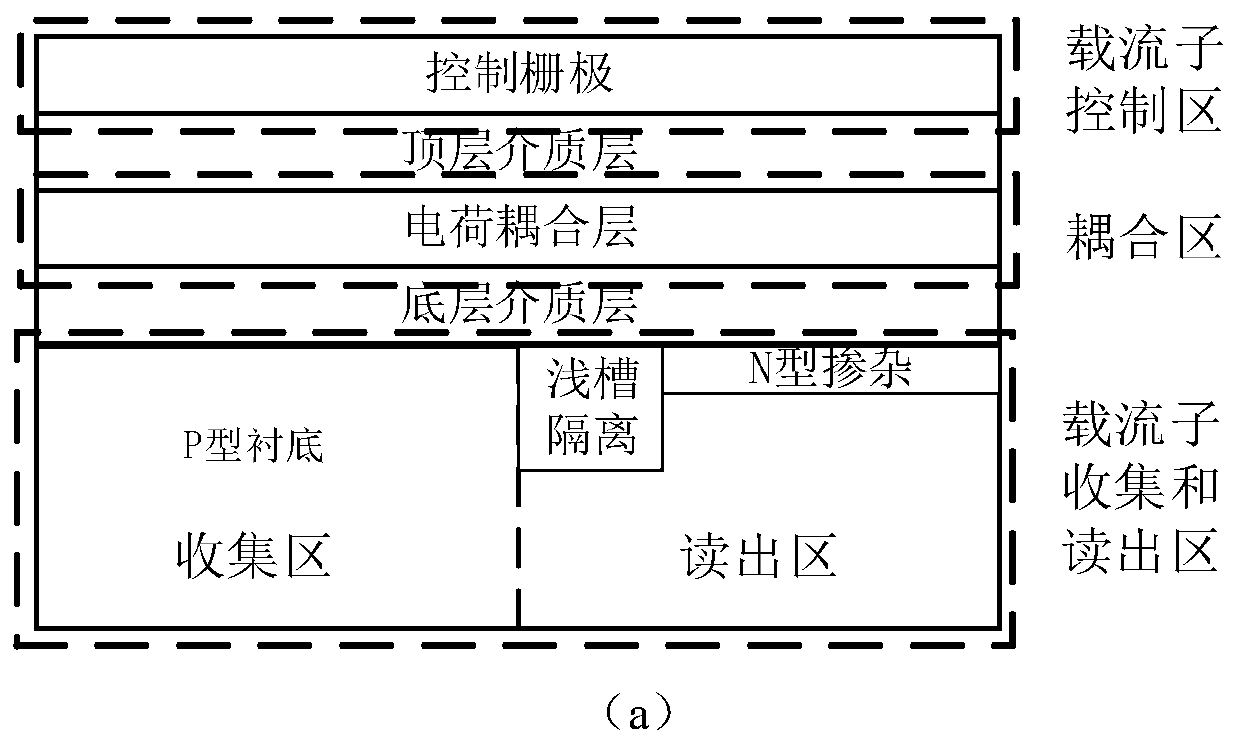

[0032] like image 3As shown, the computing unit of this embodiment includes: a control gate as a carrier control region, a charge coupling layer as a coupling region, and a P-type substrate as a photo-generated carrier collection region and a readout region. The substrate is divided into a left collecting area and a right reading area, wherein the right reading area includes shallow trench isolation, an N-type source terminal and an N-type drain terminal formed by ion implantation. The shallow trench isolation is located in the middle of the semiconductor substrate, between the collection area and the readout area. The shallow trench isolation is formed by etching and filled with silicon dioxide to isolate the electrical signals of the collection area and the readout area. The N-type source terminal is located on the side of the readout region close to the underlying dielectric layer, and is formed by doping by ion implantation. The N-type drain terminal is located on the ot...

Embodiment 2

[0038] like Figure 4 As shown, the computing unit of this embodiment includes: a control gate as a carrier control region, a charge coupling layer as a coupling region, and a P-type semiconductor substrate as a photo-generated carrier collection region and a readout region, wherein The P-type substrate includes an N-type source terminal and a drain terminal formed by ion implantation. The P-type semiconductor substrate can undertake the work of photosensitive and readout at the same time. The N-type source terminal is located on the side of the readout region close to the underlying dielectric layer, and is formed by doping by ion implantation. The N-type drain terminal is located on the other side of the semiconductor substrate near the underlying dielectric layer and opposite to the N-type source terminal, and is also formed by doping by ion implantation.

[0039] When photosensitive, a pulse with a negative voltage range is applied to the P-type semiconductor substrate, ...

Embodiment 3

[0044] like Figure 5 As shown, the computing unit of this embodiment includes: a photodiode and a readout tube serving as a collection and readout region of photogenerated carriers, wherein the photodiode is formed by ion doping and is responsible for light-sensing. The N region of the photodiode is connected to the control gate of the readout tube and the source end of the reset tube through the optoelectronic coupling lead as the coupling region, and a positive voltage pulse is applied to the drain end of the readout tube as the drive voltage of the readout current; exposure Before exposure, the reset tube is turned on, and the voltage of the drain terminal of the reset tube is applied to the photodiode, so that the photodiode as the collection area is in a reverse biased state, and a depletion layer is generated; during exposure, the reset tube is turned off, the photodiode is electrically isolated, and the photon After incident in the depletion region of the photodiode, p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More