A hardware programmable heterogeneous multi -core film system

A heterogeneous multi-core, system-on-chip technology, applied in digital computer components, general-purpose stored program computers, architectures with a single central processing unit, etc., can solve poor application adaptability, inconvenient DSP multi-core expansion, and inconvenient DSP multi-core flexibility Scheduling and other issues to achieve the effect of wide application, balanced structure, and improved flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

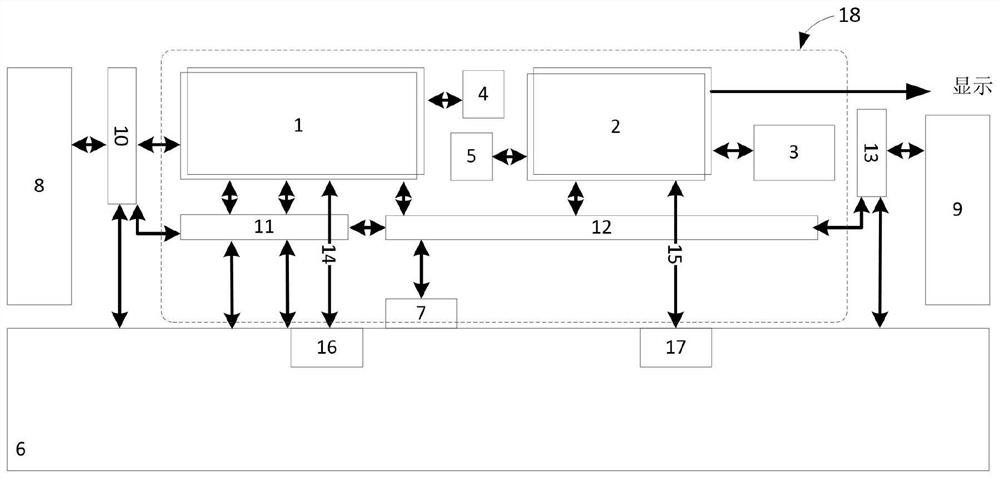

[0031]The present invention provides a hardware-programmable heterogeneous multi-core system-on-chip, such as figure 1 As shown, including multi-core DSP 1, multi-core MPU 2, GPU 3, DSP accelerator firmware 4, MPU accelerator firmware 5, FPGA 6, FPGA configuration peripheral module 7, IO peripheral A8, IO peripheral B 9 and on-chip high-speed bus interconnection connect to the network. Can realize programmable DSP accelerator 16 and programmable MPU accelerator 17 in described FPGA 6; Described on-chip high-speed bus interconnection network comprises FE bus 10, DSP-PL bus 11, PS bus 12, BE bus 13, AIP_DSP bus 14 and AIP_MPU bus 15, each functional module is connected through on-chip high-speed bus interconnection network.

[0032] read on figure 1 , the IO peripheral A 8 is connected with the multi-core DSP 1 and the FPGA 6 through the FE bus 10, and transmits data to be processed to the multi-core DSP 1 and the FPGA 6; the multi-core DSP 1 passes through the multi-core DSP ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More