Super junction device

A superjunction device and charge technology, applied in the field of semiconductor integrated circuits, can solve the problems of reducing EAS capability, EAS burning, reducing parasitic triode base current, etc., to avoid high electric field damage, simple electric field distribution, and saving chip size.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

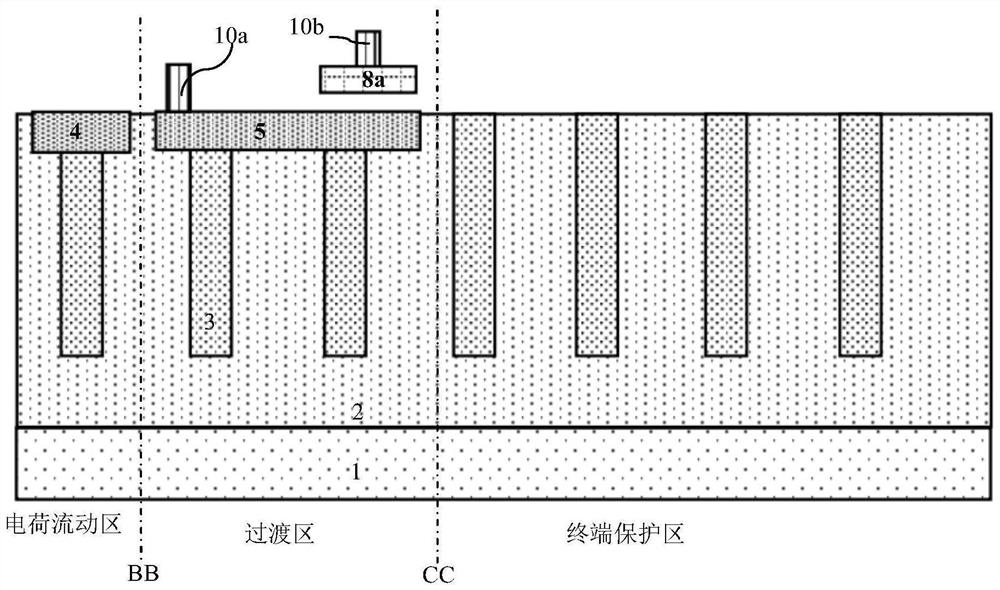

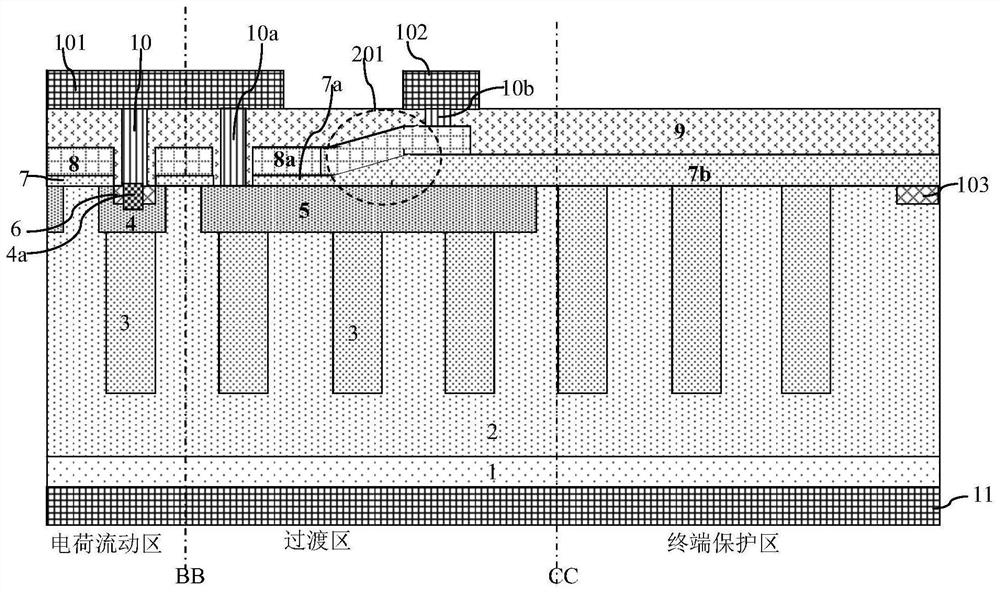

[0048] The technical solution of the embodiment of the present invention is obtained on the basis of analyzing the existing technical problems. Before introducing the technical solution of the embodiment of the present invention in detail, the structure of the existing super-junction device is described as follows, as follows figure 1 Shown is a schematic diagram of the layout structure of the existing super junction device; figure 2 yes figure 1 Schematic diagram of the cross-sectional structure of the device at the position of the AA line; image 3 yes figure 2 Schematic diagram of the cross-sectional structure of the device when the middle gate structure is a planar gate; the middle region of the existing super-junction device is the charge flow region, the terminal protection region is formed around the charge flow region, and the transition region is located between the terminal protection region and the between the charge flow regions, figure 2 In , the left side o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More