Composite substrate, composite film and preparation method thereof

A composite substrate and composite film technology, applied in electrical components, impedance networks, etc., can solve problems such as the influence of substrate materials and the insufficient trap density.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

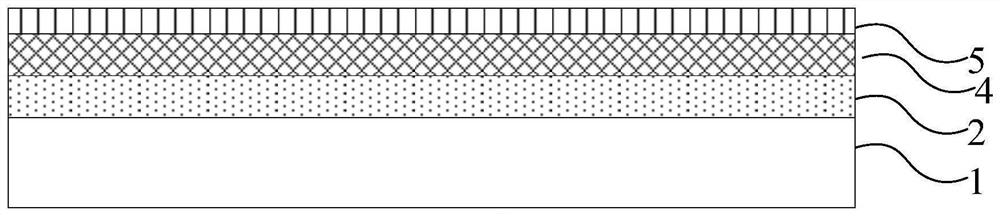

Embodiment 1

[0167] Using high-resistance silicon substrate (resistivity>2500Ω·cm) as the semiconductor substrate, using the RCA method to clean the process surface to obtain a clean surface;

[0168] Deposit a polysilicon layer as a trap layer on the process surface of the processed high-resistance silicon substrate by LPCVD process, the deposition temperature is 580°C-590°C, and the deposition thickness is 300nm;

[0169] Implant C into the polysilicon layer + Form a trap enhancement layer, adjust the implantation depth to about 100nm, the implanted ions will expand in the depth direction, and present a Gaussian distribution near the implantation depth, based on the total molar weight of the trap enhancement layer, wherein the dopant atoms The molar percentage is 5%;

[0170] The product obtained in the above steps is annealed at 700 ° C ~ 950 ° C, and the annealing atmosphere is N 2 , the annealing time is 4h, and the C element will be more uniformly distributed in the polysilicon fil...

Embodiment 2

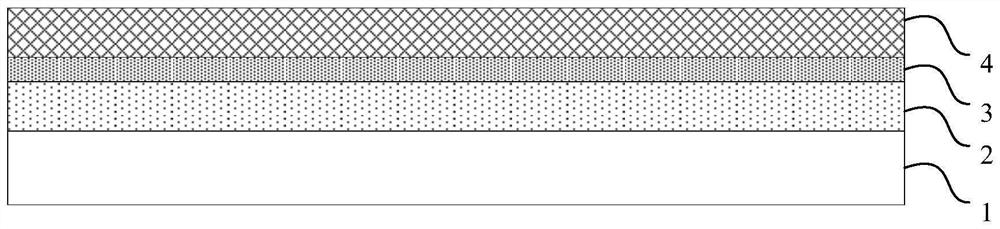

[0176] Using silicon carbide substrate (resistivity>2500Ω·cm) as the semiconductor substrate, the process surface is cleaned by RCA method to obtain a clean surface;

[0177] Deposit a polysilicon layer as a trap layer on the process surface of the processed high-resistance silicon substrate by LPCVD process, the deposition temperature is 640°C-650°C, and the deposition thickness is 3000nm;

[0178] Implant C into the polysilicon layer + Form a trap enhancement layer, adjust the implantation depth to about 500nm, the implanted ions will expand in the depth direction, and present a Gaussian distribution near the implantation depth, based on the total molar weight of the trap enhancement layer, wherein the dopant atoms The molar percentage is 30%;

[0179] The product obtained in the above steps is annealed at 700 ° C ~ 950 ° C, and the annealing atmosphere is N 2 , the annealing time is 4h, and the C element will be more uniformly distributed in the polysilicon film layer due...

Embodiment 3

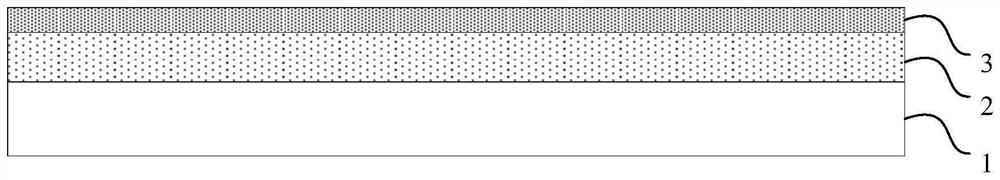

[0185] GaAs substrate (resistivity>2500Ω·cm) is used as the semiconductor substrate, and the process surface is cleaned by RCA method to obtain a clean surface;

[0186]Deposit a polycrystalline Ge layer as a trap layer on the process surface of the processed high-resistance silicon substrate by PECVD process, the deposition temperature is 200°C-500°C, and the deposition thickness is 1000nm;

[0187] Implanting Ar into the polycrystalline Ge layer + Form a trap enhancement layer, and adjust the implantation depth to about 100nm to 500nm. The implanted ions will expand in the depth direction and present a Gaussian distribution near the implantation depth. Based on the total molar weight of the trap enhancement layer, the doped The molar percentage of atoms is 0.5%;

[0188] Deposition of SiO on trap enhancement layer by PECVD method 2 film layer as insulating layer, SiO 2 The thickness of the film layer is 5 μm;

[0189] to SiO 2 The film layer is subjected to CMP treatmen...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More