Three-dimensional intelligent micro-system chip

A microsystem and chip technology, which is applied in the components of TV systems, microstructure technology, microstructure devices, etc., can solve the difficult wafer-wafer three-dimensional integration process, increase the difficulty of intelligent microsystems, and difficult to integrate traditional sensors, etc. problems, to achieve the effect of improving R&D efficiency, lowering test costs, and reducing chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

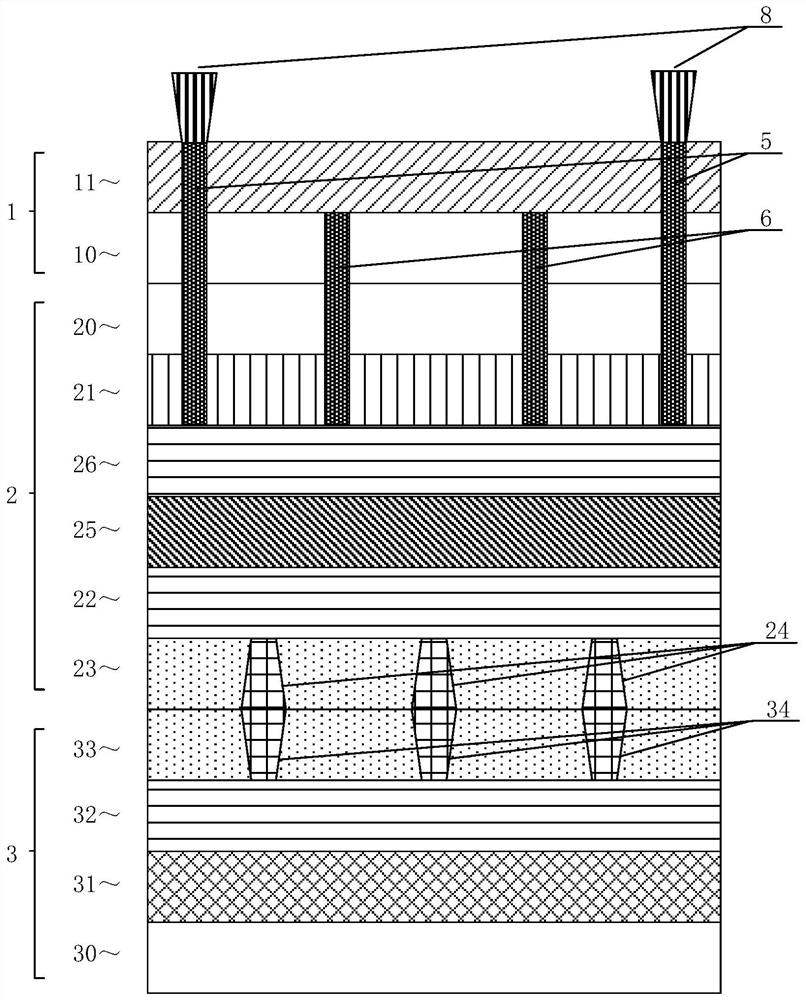

[0057] figure 1 A schematic structural diagram of a hierarchical storage scheme (new type) of a three-dimensional intelligent microsystem chip provided in this embodiment, the chip includes:

[0058] The first chip 1; including a first sensing layer 11 and a fourth substrate 10; the fourth substrate 10 is stacked on the first sensing layer 11;

[0059] The second chip 2; includes a first substrate 20, a first active region layer 21, a first metal layer 22, a first dielectric layer 23 and a first through hole 24; wherein, the number of the first through hole 24 can be One, or multiple; the first substrate 20, the first active region layer 21, the first metal layer 22 and the first dielectric layer 23 are sequentially stacked and connected, and the first through hole 24 is provided in the first dielectric layer 23, the first through hole 24 connects the first metal layer 22 and the outside of the first dielectric layer 23, and the first through hole 24 is the input end or outp...

Embodiment 2

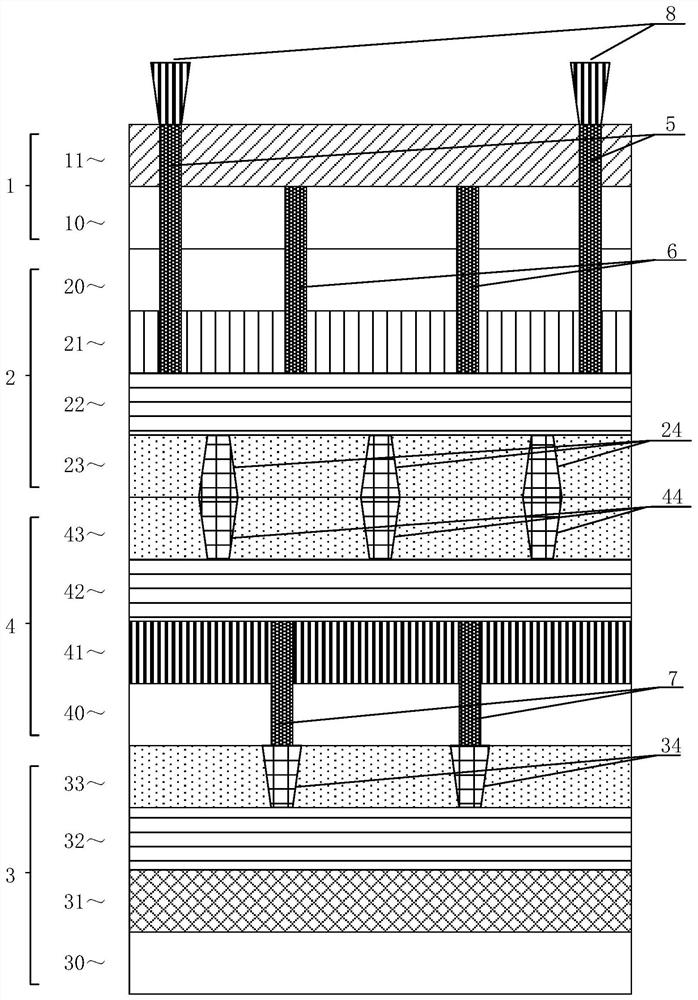

[0067] figure 2 A schematic diagram of a hierarchical storage scheme (traditional) structure of a three-dimensional intelligent microsystem chip provided in this embodiment, the chip includes:

[0068] The first chip 1; including a first sensing layer 11 and a fourth substrate 10; the fourth substrate 10 is stacked on the first sensing layer 11;

[0069] The second chip 2; includes a first substrate 20, a first active region layer 21, a first metal layer 22, a first dielectric layer 23 and a first through hole 24; wherein, the number of the first through hole 24 can be One, or multiple; the first substrate 20, the first active region layer 21, the first metal layer 22 and the first dielectric layer 23 are sequentially stacked and connected, and the first through hole 24 is provided in the first dielectric layer 23, the first through hole 24 connects the first metal layer 22 and the outside of the first dielectric layer 23, and the first through hole 24 is the input end or ou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More