Manufacturing method of high-voltage thick gate oxide

A manufacturing method and thick gate oxide technology, which are applied in semiconductor/solid state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems affecting the reliability of thick gate oxide related device performance, poor reliability of thermal oxide growth, and thin gate oxide. and other problems, to achieve the effect of improving reliability and performance of high-voltage devices, low cost, and eliminating sharp corners.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0040] The manufacturing method of high-voltage thick gate oxide includes the following steps:

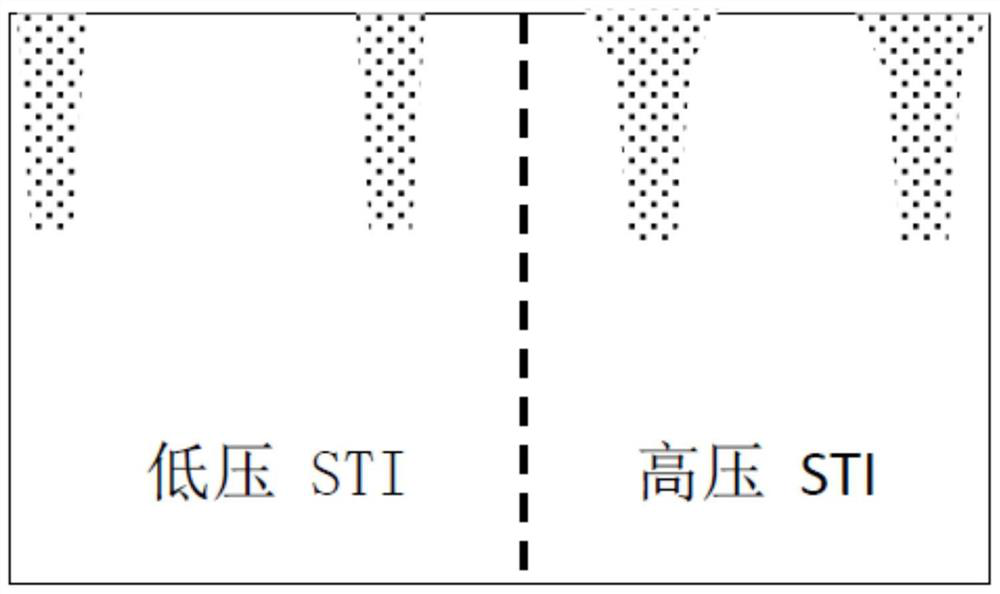

[0041] 1. Deposit a pad layer silicon oxide (PAD Oxide) 11 on the silicon substrate 1, and deposit a pad layer silicon nitride (PAD SIN) 21 on the pad layer silicon oxide 11; perform shallow trench isolation (STI) photolithography and etching ; Perform shallow trench isolation (STI) silicon oxide filling and chemical mechanical polishing (Oxide Filling and CMP), such as Figure 4 shown;

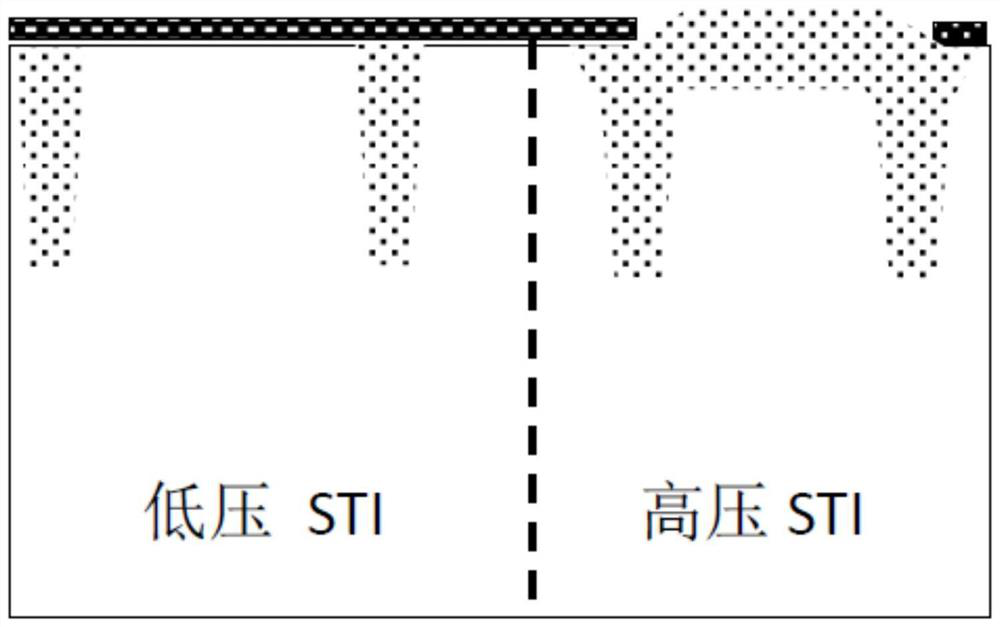

[0042] 2. Deposit mask silicon nitride 22 on the silicon wafer, and deposit mask silicon oxide 12 on the mask silicon nitride 22;

[0043] 3. Using the mask silicon oxide 12 as a hard mask, photolithography and etching remove the mask silicon oxide 12 and mask silicon nitride 22 in the high-voltage thick gate oxide region, and retain the two shallow grooves in the high-voltage thick gate oxide region Pad silicon nitride 21 between isolation (STI), such as Figure 8 shown;

[0044] 4. Perform t...

Embodiment 2

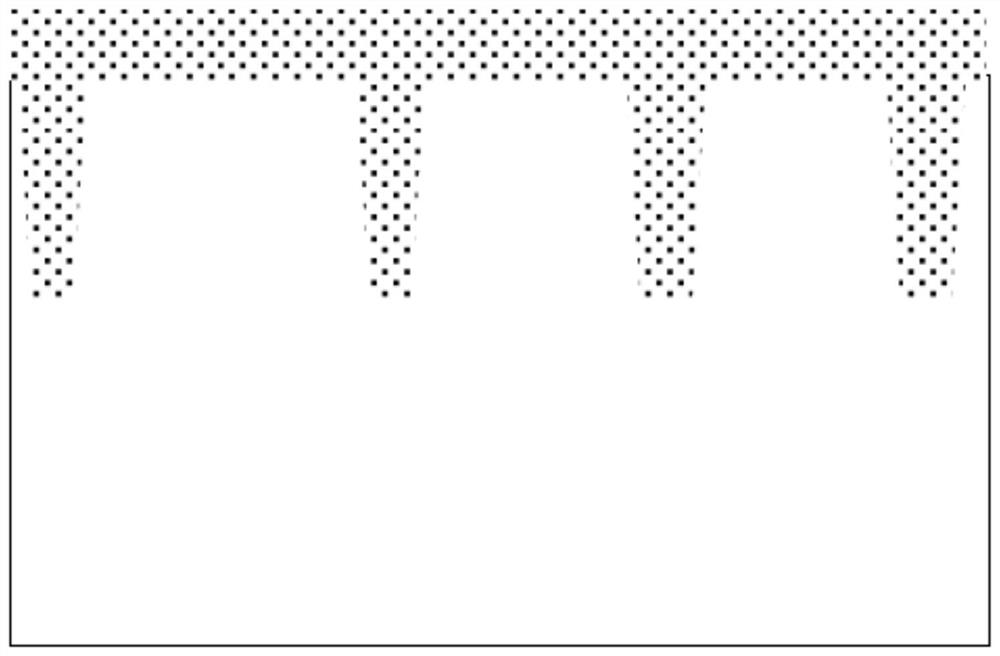

[0050] Based on the manufacturing method of high-voltage thick gate oxide in Embodiment 1, after step 5, the pad layer silicon oxide 11 on the silicon substrate 1 between the two shallow trench isolations and the mask silicon nitride outside the high-voltage thick gate oxide region are removed The mask silicon oxide 12 on 22 is cleaned, and then step six is performed;

[0051] In step six, a second thermal oxidation growth is performed on the silicon substrate 1 in the high-voltage thick gate oxide region to generate high-voltage thick gate oxide.

[0052]The manufacturing method of the high-voltage thick gate oxide of the second embodiment is to remove the pad silicon oxide 11 deposited on the silicon substrate 1 between the two shallow trench isolations (STIs), and then place the pad silicon oxide 11 on the silicon substrate 1 The high-voltage thick gate oxide is generated through the second thermal oxidation growth, which can reduce the impurities of the high-voltage thic...

Embodiment 3

[0054] Based on the manufacturing method of high-voltage thick gate oxide in Embodiment 1, wet oxygen oxidation, water vapor oxidation or dry oxygen oxidation is used for the first thermal oxidation growth;

[0055] The second thermal oxidation growth adopts wet oxygen oxidation, water vapor oxidation or dry oxygen oxidation.

[0056] Preferably, dry oxygen oxidation is used for the first thermal oxidation growth, and the passivation effect is good; wet oxygen oxidation or water vapor oxidation is used for the second thermal oxidation growth, and the oxidation speed is fast.

[0057] Preferably, the first thermal oxidation growth uses a wet oxygen oxidation process, the operating temperature of the wet oxygen oxidation process is 800°C to 900°C (for example, 850°C), and the oxygen flow rate is 24 to 26 liters / minute (for example, 25 liters / minute ), the flow rate of hydrogen is 26~28 liters / minute (for example 27 liters / minute). In the wet oxygen oxidation process, oxygen can...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More