VCSEL chip and preparation method thereof

A chip and silicon nitride layer technology, applied in laser parts, electrical components, lasers, etc., can solve the problems of attenuation, chip efficiency reduction, influence of chip resistance value, etc., to reduce internal resistance and improve optical performance. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0029] The preparation method of the above-mentioned high-efficiency VCSEL chip is as follows:

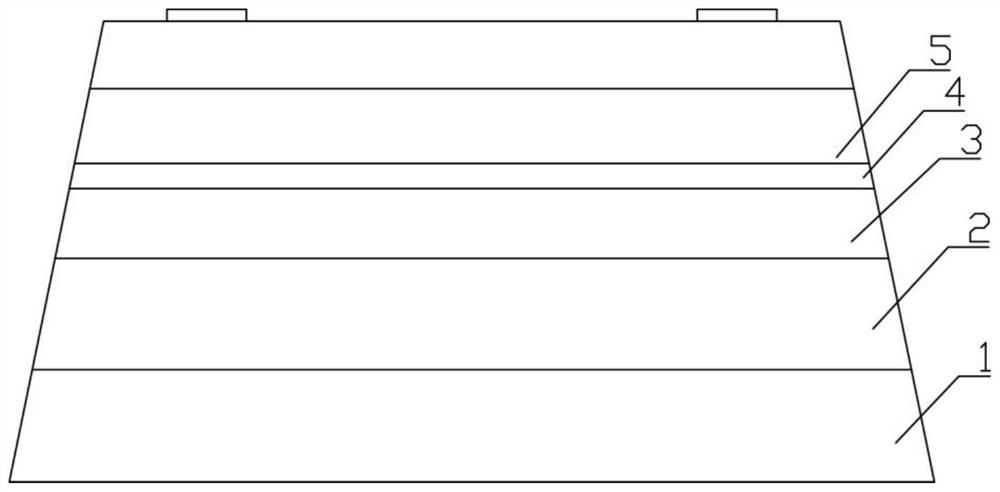

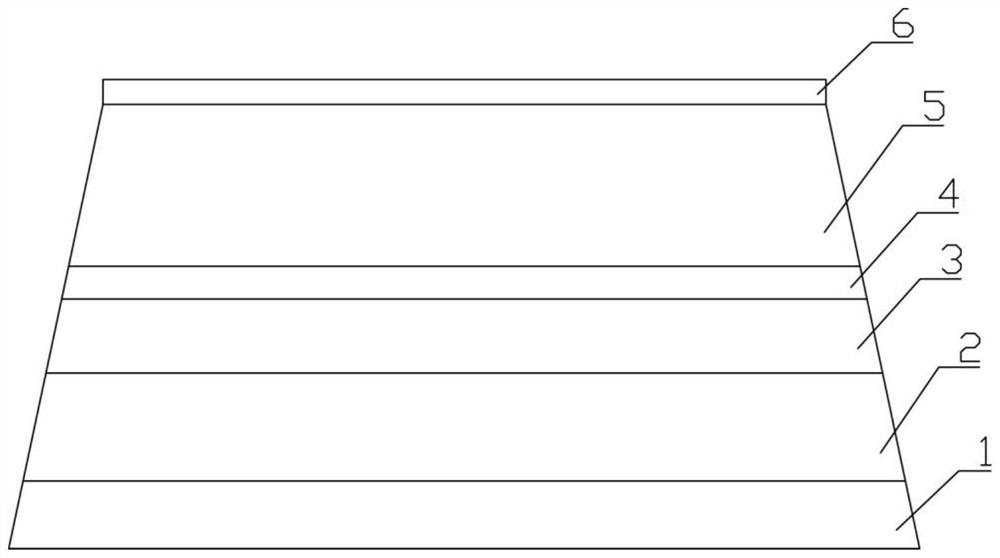

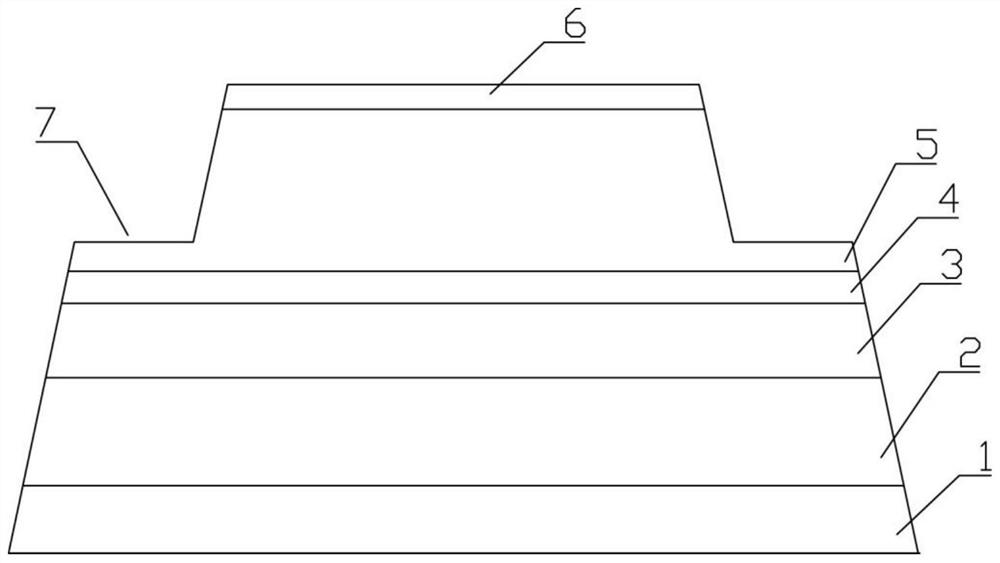

[0030] S1: GaAs substrate 1 is provided, and N-DBR structure 2, MQW active layer 3, oxide layer 4 and P-DBR structure 5 are sequentially grown on GaAs substrate 1 according to conventional methods;

[0031] S2: Using a PECVD machine to deposit silicon nitride on the P-DBR to form the first silicon nitride layer 6 by conventional methods, such as figure 2 shown;

[0032] S3: if image 3 As shown, the first silicon nitride layer 6 and the P-DBR structure 5 are etched until the P-DBR structure 5 has 2-3 pairs of DBR layers left to form a mesa 7;

[0033] S4: if Figure 4 As shown, C or Ge material is deposited on the mesa 7 to obtain a P-contact ring 8;

[0034] S5: if Figure 5 As shown, the second silicon nitride layer 9 is obtained by depositing silicon nitride from the GaAs substrate 1 up to the first silicon nitride layer 6 according to a conventional method;

[0035] S6: ...

Embodiment 2

[0038] In addition, the P-contact ring 8 can also be obtained through secondary epitaxy of a highly doped layer. The specific method is as follows:

[0039] S1: GaAs substrate 1 is provided, and N-DBR structure 2, MQW active layer 3, oxide layer 4 and P-DBR structure 5 are sequentially grown on GaAs substrate 1;

[0040] S2: Depositing silicon nitride on the P-DBR to form a first silicon nitride layer 6;

[0041] S3: Etching the first silicon nitride layer 6 and the P-DBR structure 5 until the P-DBR structure 5 has 2-3 pairs of DBR layers left to form the mesa 7;

[0042] S4: A P-contact ring 8 is obtained by secondary epitaxial highly doped layer on the mesa 7;

[0043] S5: Etching away the highly doped layer other than the P-contact ring 8, and then depositing silicon nitride from the GaAs substrate 1 up to the first silicon nitride layer 6 to obtain the second silicon nitride layer 9;

[0044] S6: Etching the second silicon nitride layer 9 to the P-contact ring 8 to obtai...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More