Deep-shallow combined Schottky barrier tunnel transistor and manufacturing method thereof

A technology of tunnel transistor and Schottky potential, which is applied in the deep and shallow combined Schottky barrier tunnel transistor and its manufacturing field, can solve the problems of large static power consumption, high sub-threshold swing, large leakage, etc. consumption, suppression of reverse leakage current, suppression of the effects of large

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

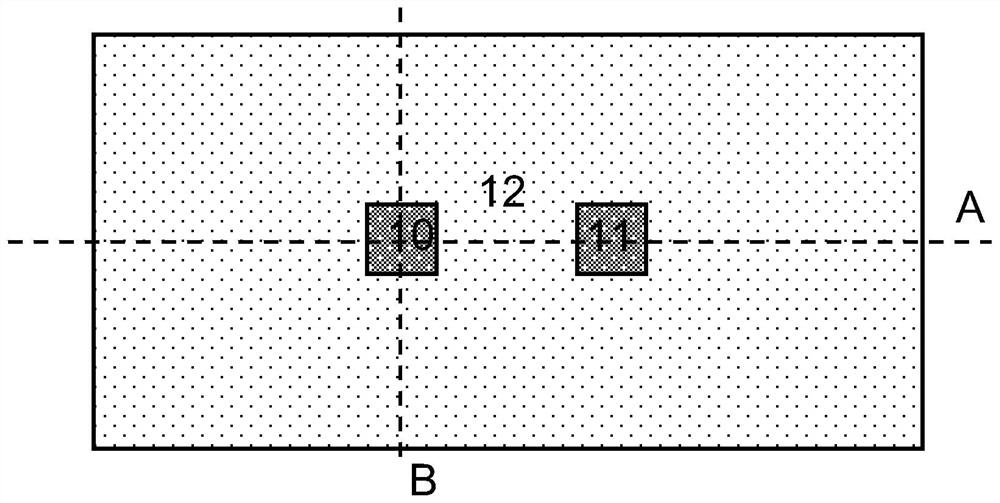

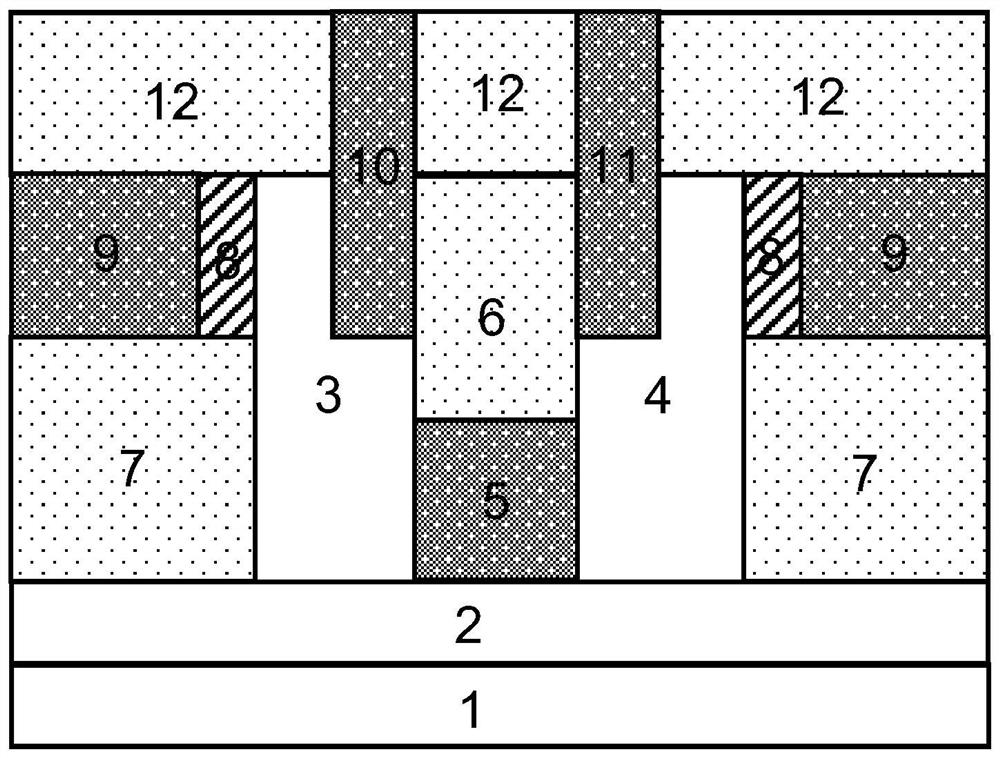

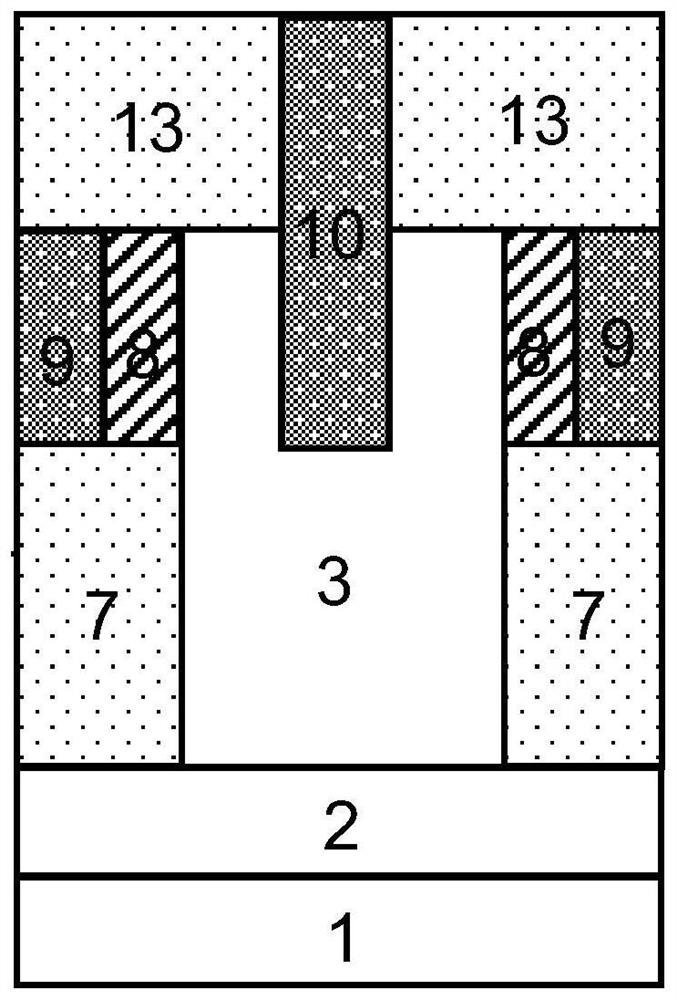

[0054] A deep and shallow combined Schottky barrier tunnel transistor, comprising a silicon substrate 1 of an SOI wafer, a substrate insulating layer 2 of the SOI wafer above the silicon substrate 1 of the SOI wafer, and a substrate insulating layer of the SOI wafer Above 2 are single crystal silicon film a3, single crystal silicon film b4, central metal region 5 and embedded dielectric barrier layer 6; wherein, single crystal silicon film a3 and single crystal silicon film b4 have an impurity concentration lower than 10 16 cm -3 single crystal silicon semiconductor material; the central metal region 5 is located at the bottom between the single crystal silicon film a3 and the single crystal silicon film b4; the left and right sides of the central metal region 5 are respectively connected to the single crystal silicon film a3 and the single crystal silicon films b 4 are in contact with each other;

[0055] For the deep-shallow combined Schottky barrier tunnel transistor used...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More