Ferroelectric FET and its preparing process

An electric field effect and transistor technology, which is applied in the field of microelectronic devices, can solve problems such as fatigue and poor interface characteristics, and achieve the effects of simplifying the process, improving the yield, and realizing non-volatile storage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019]The present invention will be described in further detail below in conjunction with the accompanying drawings.

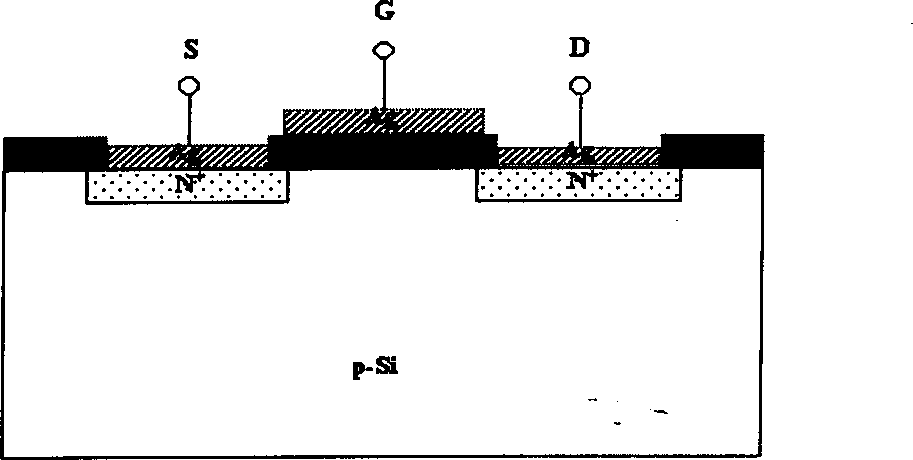

[0020] Such as figure 1 As shown, the ferroelectric field effect transistor can be divided into several identical unit segments, and the unit segment is composed of a substrate 1, a source region 2, a drain region 4, and a gate region 3 between the source region 2 and the drain region 4, The substrate 1 is a P-type single crystal silicon wafer with a (100) crystal orientation, and the source region 2 and the drain region 4 are N + The ion implantation area is embedded in the surface of the substrate 1, and the gate area 3 is bismuth titanate Bi 4 Ti 3 o 12 The thin film is located on the upper surface of the substrate 1, and there is a layer of Ag electrodes on the surfaces of the source region 2, the gate region 3 and the drain region 4, which form the source electrode 5, the gate electrode 6 and the drain electrode 7 respectively.

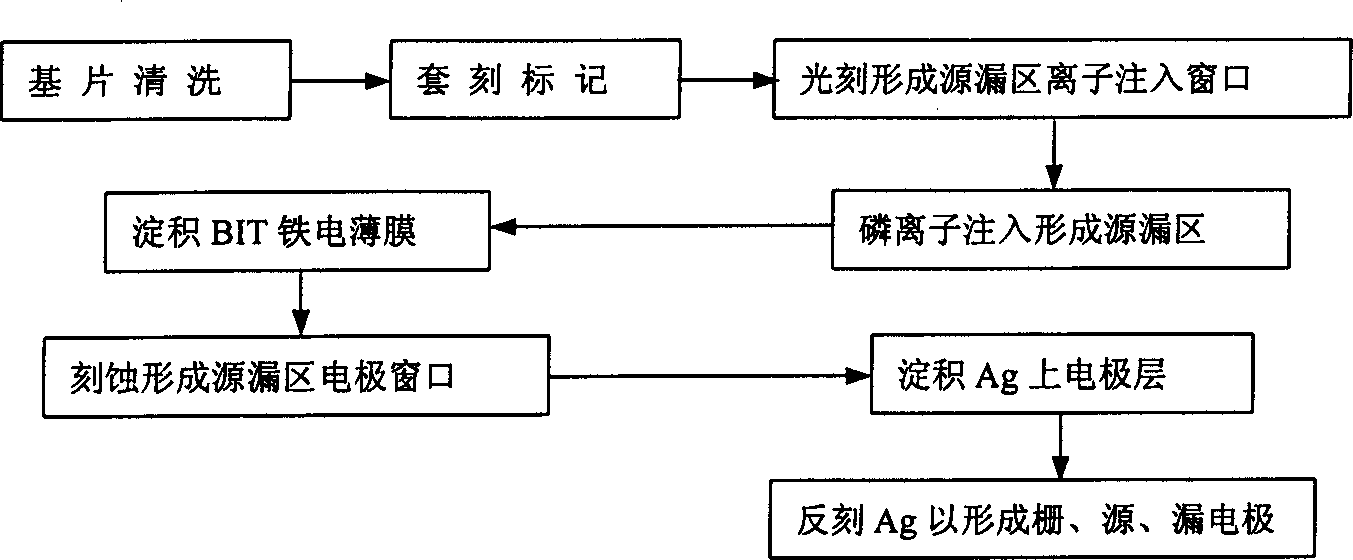

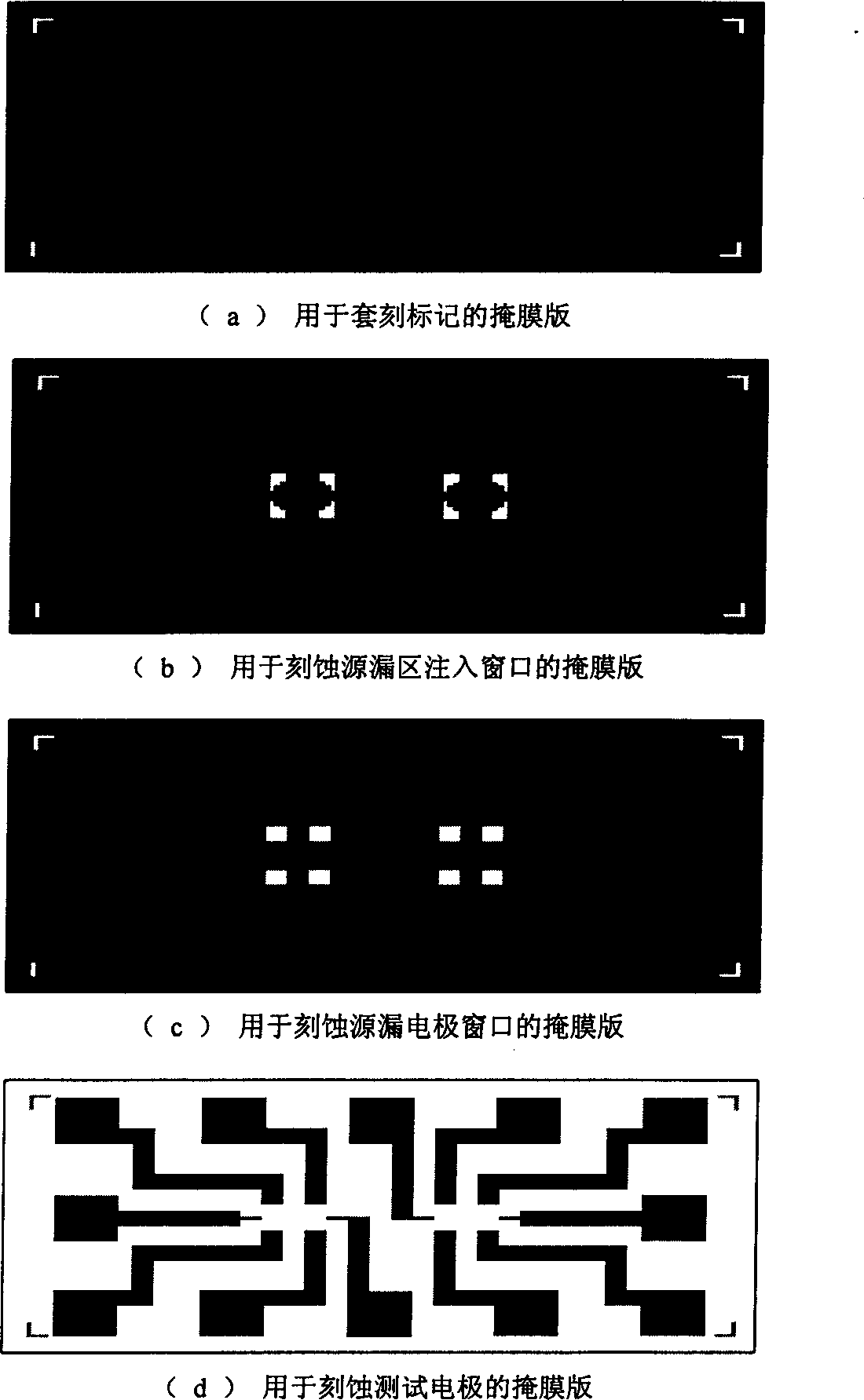

[0021] The preparatio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More